|

아날로그필터와 OPAMP

Op Amp. 사용설명서 PART 2

글 | (주)싱크웍스 백종철

본 글은 “아날로그필터와OPAMP, ㈜싱크웍스 출판사, 백종철” 책자에서 자칫 많은 개발자들이 그 중요성을 간과 하기 쉽지만 실전에서 꼭 필요한 OPAMP에 대한 내용을 디바이스마트 매거진 독자들을 위해 발췌하여 수록하였습니다. |

목차

1. Op Amp. 실제 부품의 이해와 핀 설명

2. Op Amp.의 전원 공급과 전류의 흐름

3. Rail to Rail Input Output(RRIO) 방식의 장점

4. CMRR과 PSRR

5. Loading Effect (부하의 영향)

6. �Instrumentation Amplifier

(정밀 기기용, 계측용 증폭기)

7. Op Amp.의 Sense 핀과 Ref. 핀의 사용법

8. �단전원(Single Power Supply) 조건에서

Op Amp. 구동

9. Fully Differential Op Amp. (FDA)

지난 호의 PART1에 이어서 능동 필터의 핵심 소자로 사용되는 Op Amp.에 대한 내용을 다룬다. 쓰다 보니 양이 너무 많아져서, 취사 선택을 해야만 했다. 첫번째 기준으로는 FilterPro 사용에 있어서 부족함이 없도록. 둘째는, 현장에서 흔히 놓치는 Op Amp.의 중요한 성질들을 확실히 다루자 라는 것이었다. 아울러 실제 부품을 사용했을 때 발생 가능한 현상들을 TINA를 통해서 확인하는 과정을 곳곳에 배치했기에, 현 업무에 직접적으로 도움이 될 것이다. 마지막으로는, 최근 들어 주목받고 있는 FDA(Fully Differential op Amp.)를 다뤄봤다. 막상 별다를 바가 없다는 것을 이해하실 수 있을 것이다.

5. Loading Effect (부하의 영향)

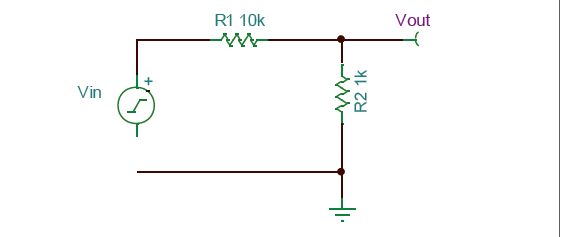

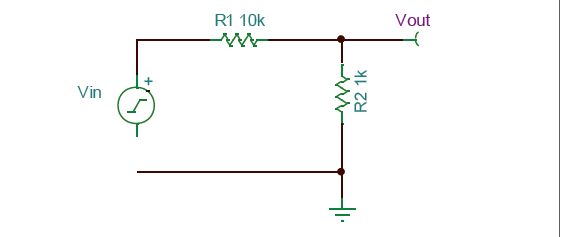

이상적인 연산증폭기는 전압이득이 무한대이며, 입력 임피던스 또한 무한대, 출력 임피던스는 0인 전압 증폭기의 일종으로 아날로그 컴퓨터의 핵심 소자 중의 으뜸이라고 다들 열심히 배웠고, 열심히 사용중이신 분들도 계실 것이다. 연산증폭기를 다루기 시작했거나, 전압 증폭기라는 것을 처음 접하시는 분들은 앞서 언급한 성질이 왜 이상적인 것인지 납득하기 어려우실 것이다. 80여년 전에, 미국의 뉴욕에 사셨던 Harry Black이라는 선배님이 뉴져지 주에 있는 벨 연구소로 기차타고, 페리호타고, 출퇴근하시면서 고안해낸 개념이라고 한다. 이런 개념을 왜 만들었을까? 그 당시의 최첨단 기술이었던 전화와 관련있다. 장거리 전화를 할려니 증폭기가 필요했고, 이게 문제가 많았다. 즉, 부하문제를 증폭기로 해결할려고 시도하였다. 부하가 야기하는 문제를 정확히 이해하는 것이 어떤 측면에서는 증폭기를 다루는 핵심이기도 하다. 다음을 상상해보자. 그림 5-1 회로에서 Vout을 계측기의 프루브(탐침, probe)를 이용해 측정하고자 한다. 둘러보니, 프루브가 두 종류가 있는 것이 아닌가? 하나는 임피던스가 1K옴이고, 다른 하나는 10M옴이다. 어떤 것을 쓰겠는가? 시간적 여유가 충분해서 둘 다 이용해서 측정해 보았다.

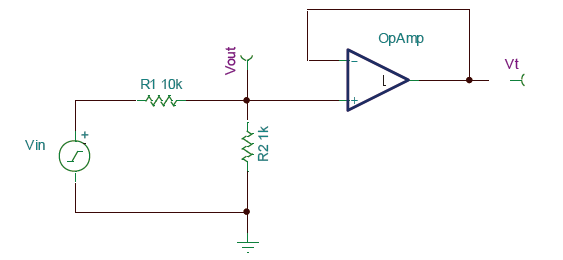

그림 5-1. 측정 대상 회로. 측정 지점 : Vout 그림 5-1 회로에서 Vout은 R1-R2 직렬저항에 의한 전압 분배로 Vin의 1/11이 됨을 쉽게 알 수 있다. 계측기라고 한다면 이 값을 정확히 표시해 주어야 할 것이다. 먼저, 1K옴의 입력 임피던스를 가지는 프루브를 가져다 대었다. R2와 병렬로 프루브 내부 1K옴 저항이 연결되기에 Vout은 V_in·(1k||1k)/(10k+1k||1k)가 되어서, 결과적으로 Vin·5/105, 즉, Vin·1/21로 계산치와 거의 50%에 육박하는 오차가 발생한 것이다. 이러한 현상을 Loading Effect(부하의 영향)라고 한다.

이제는 1M옴 프루브로 측정해보자. Vout은 V_in·(1k||1M)/(10k+1k||1M)가 된다. 1M옴 프루브로 인한 오차는 약 0.091%이다. 만약 임피던스가 10M옴인 프루브를 사용한다면, 약 0.0091% 가 된다. 전압 신호를 손실없이 전달하기 위해서는 전달 매개체의 입력 임피던스가 일단은 무진장하게 커야 한다는 것을 짐작할 수 있을 것이다. 이상적인 증폭기의 입력 임피던스가 무한대이어야 하는 근거다. 달리 말해, 원 회로에 최대한 부담을 적게 주고, 즉, 전류를 아주 조금만 뽑아서 측정하겠습니다 라는 점이다. 전류를 아주 적게 뽑아서 쓰겠다면? 그래 그거야, Op Amp.의 입력 저항이 무한대가 아니던가, 게다가, 입력 전류가 0 이니… 딱이군. 그렇다면, ‘실제 Op Amp. 라면, 입력단이 FET(Field Effect Transistor, 전계 효과 트랜지스터)로 구현되어 있는 것이라면 더욱더 좋겠군’ 하고 짐작들 하실 것이다. 그렇다. 이론적으로는, FET의 입력 임피던스가 무한대이다. 하지만, BJT(Bipolar Junction Transistor)로 구현된 연산 증폭기도 입력 임피던스를 매우 높게 설정하여 설계하므로 Loading effect를 크게 걱정하지 않아도 된다. 대부분의 전자회로 교과서에서 소개하는 741 연산 증폭기는 입력단이 BJT로 되어 있으며, 통상적인 입력 임피던스는 약 2M옴이다. 앞서 살펴보았듯이, FET로 구현된 TLC2274의 입력임피던스는 1테라옴이다. 2M옴도 충분히 크지만, 1테라옴은 환상적이다.

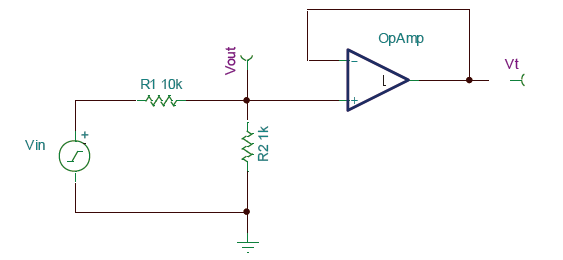

지금까지는 프루브로 측정한 결과를 논하였는데, 이제는 그림 5-1의 Vout을 다른 회로부에 전달해야 하는 경우를 고려해보자. 하필이면, 전달하고자 하는 회로부의 입력 임피던스가 1K옴이며 이를 변경하는 것은 불가능하다고 하자. 앞서 1K옴 프루브로 측정한 사례처럼, 바로 연결했다가는 신호 손실이 50% 가까이 발생할 것이다. 전달 매개체가 필요하다. 어떤 것이 좋을까? 이럴 때 이상적인 연산증폭기가 딱이다. 그림 5-2를 보자.

그림 5-2. Voltage Follower 또는 아날로그 버퍼 그림 5-2 회로에서 Vt와 Vout의 차이는 거의 측정할 수 없는 수준이다. 위 회로에 사용된 연산증폭기의 결선 형태를 흔히들 Voltage Follower라고 한다. 출력 전압의 변화가 입력 전압 변화를 그대로 따라가기 때문에 이런 말을 쓰는데, Impedance Matcher 라고도 하고, 아날로그 버퍼라고도 많이 불린다. 그 이유를 하나씩 살펴보자. 그림 5-2 회로에서는 Vout 지점에서 바라본 출력 임피던스가 10K||1K 로 고정되어 있다. Vout을 전달 받을 시스템의 입력 임피던스는 최소 10배 이상, 가능하다면 100배이상이 된다면 더할 나위 없이 좋겠다. 하지만, 출력 임피던스가 시시각각으로 변하는 장치들도 많다. 대표적인 것이 생체(生體)다. 출력 임피던스가 시시각각으로 변하는 장치로부터 신호를 받아내려면 어떻게 해야할까? 측정 장치 혹은 신호 수신 장치의 입력 임피던스가 무식하게 크면 걱정할 필요가 없을 것이다. 즉, 이상적인 증폭기의 입력 임피던스가 무한대인 이유다. 그림 5-2 회로에 이상적인 Op Amp.가 비반전 증폭기 형태로 결선되어 있는 것도 바로 이런 이유다.

정리하자면, 입력 임피던스가 매우 큰 연산증폭기는 Loading effect를 최소화할 수 있다. 아날로그 버퍼 혹은, Voltage Follower 혹은 Impedance Matcher가 손실 없는 신호 전달을 도모해준다 점을 잘 기억해주시기 바란다. 그런데, Op Amp.가 신호를 수신하는데 있어서 높은 입력 임피던스로 부하효과를 최소화한다 라는 것은 알았는데, Op Amp.가 다른 시스템에 신호를 전달하는데 있어서는 어떤 역할을 할까? 하나씩 살펴보자.

이제 그림 5-2 회로가 Vt를 최종 수신 회로에 전달해야 한다. 신호를 전달하려는 곳의 임피던스가 1K 옴이라고 했으며, 고정이라고 했다. Vt가 손실없이 고스란히 수신부에 전달이 되려면, Vt에서 바라본 Op Amp.측의 출력 임피던스가 수신측 입력 임피던스인 1K옴보다 최소 10배, 더 좋게는 100배이상 작아야 Loading Effect가 무시할 수준으로 작아질 것이다. Op Amp.의 출력 임피던스가 얼마면 되겠는가? 연산증폭기의 산 조상격인 741 Op Amp.의 출력 임피던스는 통상 75옴이다. 최신 연산 증폭기는 이보다 대체로 작다. 적용하고자 하는 Op Amp.의 출력 임피던스가 75옴이라면, 수신측 입력 임피던스가 1K옴이기에 10배이상 충분히 작다. 정밀 시스템이 아닐 경우, 10배 이상의 차이를 보이면 어느 하나의 영향을 무시할 수 있는 것이 엔지니어링의 배포이기도 하지 아니한가. 이런 식이다. 1K옴과 10K옴의 저항이 병렬로 연결되어 있다면, 둘 차이가 10배가 나기에 등가 저항값은 약 1K옴이다 라고 얘기하는 것이다. 1K옴과 10K옴이 직렬로 연결되어 있으면 그냥 10K옴인 것이다. 이런 배포도 있어야 한다. 하지만, 분위기 살펴가면서 해야 한다. 무시할 수 없는 경우를 잘 찾아내는 것도 엔지니어링 센스이니 감을 잘 키워야 한다. 만약, 출력 임피던스가 75옴 가지고는 부족하다 싶으면, 어떻게 해야 하겠는가? 출력 임피던스가 작은 Op Amp.를 찾던가 해야 한다. 검색 작업은 잠시 보류하고, 다음 회로의 입력 임피던스를 한 번 구해보자.

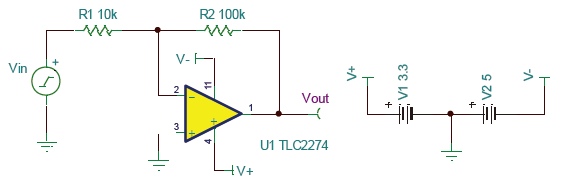

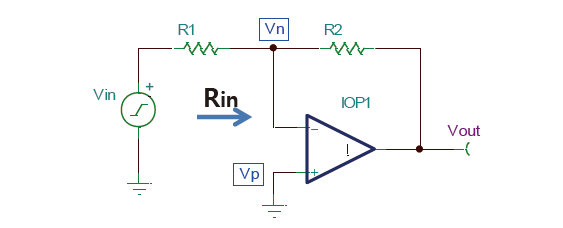

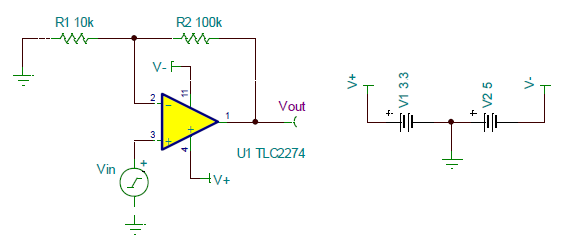

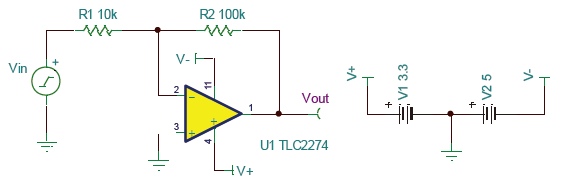

그림 5-3. 이 회로의 입력 임피던스는? TLC2274의 입력 임피던스가 1테라옴이니, 그림 5-3 회로의 입력 임피던스도 1테라옴이다. 라고 생각한다면 큰 오산이다. 회로를 다시 한 번 잘 보자. 그림 5-3의 입력 임피던스를 구하기 위해서는 그림 5-4가 도움을 줄 수 있다.

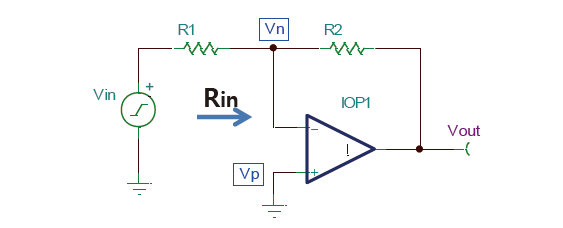

그림 5-4. 그림 5-3 회로의 입력 임피던스, Rin 구하기용 등가회로 입력 임피던스를 구하는데 불필요한 요소는 제거했으며, TLC2274보다 입력 임피던스가 더 큰 이상적인 Op Amp.로 대체 했다. 그렇다면, 그림 5-4의 입력 임피던스는 무한대인가? 흥분을 가라앉히고, 회로를 찬찬히 뜯어보자. 그림 5-4에서 Vn의 값은 얼마인가? Vp가 0V이니 Vn도 0V이다. 즉, 접지와 같다. 따라서, 입력 임피던스 Rin = R1 = 10K옴이다. 이건 뭔가? 분명히 Op Amp.의 입력 임피던스는 굉장히 크다고 했는데, 이 회로는 왜 이 따위란 말인가? 안타까운 일이지만 어쩔 수 없다. 한가지 재미난 점은, 입력 임피던스가 증폭기가 아니라 외부에 사용된 저항에 의해서 결정되었다는 점인데, 배신감에 이게 재밌을까? 하는 걱정이 든다. 정신 추스리고 다음 회로의 입력 임피던스를 한번 더 구해보자.

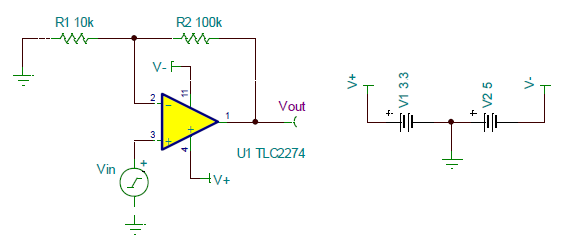

그림 5-5. 이 회로의 입력 임피던스는 얼마인가? 그림 5-5 회로의 입력 임피던스는 얼마인가? TL2274 가 사용되었으니, 그렇다. 1테라옴. 이해가 되시는가? 그림 5-5에서, TLC2274의 3번 입력 핀을 보면 흐르는 전류가 없다. 사실은 1pico 암페어 정도. 따라서, 입력 임피던스는 Vin 나누기 전류, 따라서 테라옴이 계산된다. 높은 입력 임피던스가 요구되면 그림 5-5와 같은, 즉, 비반전 형태의 결선을 이용해야 하겠다. 사실 아날로그 버퍼도 이 부류이다. 그렇다면, 그림 5-4와 같은 회로 결선은 사용을 지양해야 할까? 그림 5-4는 그 유명한 반전 증폭기 아닌가? 대부분의 전자회로 교과서나 Op Amp. 교과서 초반부에 등장하는 그 유명한 반전 증폭기 아닌가? 반전 증폭기가 막판에 와서 배신을 때리다니, 분하다. 하지만, 증폭기(비반전 증폭기) 회로의 단점도 있다. 이 회로는 이득을 1 이하로 만들 수가 없다. 또한 정확한 입력 임피던스를 만들 수가 없다. 따라서, 적재 적소에 투입할 수 있는 역량을 키워야 한다. 별 무리없이 Op Amp.를 사용하시고 싶다면, 비반전 증폭기 형태를 사용하시는 것이 무탈하겠다. 이 결선의 단점은 감쇠가 불가능하다는 점과, 이전호 4.4절에서 다뤘던 CMR 기능 활용이 반전 증폭기보다 조금 못하다라는 점인데, 다음 문단에서 설명했다.

반전 증폭기의 장점은 이해하기 쉽다라는 점이 으뜸일 듯 하다. Op Amp. 두 입력단 중에 하나가 접지로 연결되어 있으니, 풀이가 쉽다라는 장점이 있다. 그래서, 비반전 증폭기보다 먼저 다루는 듯 하다. 하지만, 좀 더 깊이 생각해보면, 반전 증폭기와 비반전 증폭기의 증폭 형태가 다르다라는 점을 발견할 수 있을 것이다. 그림 5-5와 같은 증폭기는 전압을 감지해서 전압을 증폭하는 Voltage Amplifier 이다. 하지만, 그림 5-4와 같은 반전증폭기는 엄밀히 말해, 전류를 감지해서 전압을 만들어 내는 Trans-Resistance Amplifier이다. 따라서, 어떤 증폭기 형태가 요구되는지에 따라 선택하면 되겠다.

현장에서는 반전 증폭기류를 많이 사용하는 듯 한데, 아마도 교과서에 초반부에 나와서 그런 것이 아닌가 싶다. 다들 책 사면 처음 몇 페이지는 보지 않나. 그리고, 반전 증폭기에는 단점이기도 하고 장점이기도 한 부분이 있다. 바로, 입력 임피던스를 정확하게 결정할 수 있다는 점이다. 물론, 비반전 증폭기에서도 입력단에 저항 회로를 연결하여 입력 임피던스를 정할 수는 있지만, 부품이 많이 쓰이는 단점이 있다. 세부적으로는 반전 증폭기가 동상 노이즈에 강한 편이다. 그건 바로 접지의 힘이다. 접지는 노이즈에 매우 강하다. 강하다라는 말의 의미를 정량적으로 풀어 설명하기는 좀 어렵다. 암튼 노이즈를 다 끌어안아도 접지는 접지다. 그래서, 접지는 노이즈에 강하다. 반전 증폭기 결선의 경우 Op Amp. 입력단 중 하나는 반드시 접지에 물린다. 따라서, 제대로 된 CMRR을 기대할 수 있다. 하지만, 단 전원이나 DC Offset이 필요한 경우에는, 반전 증폭기나 비반전 증폭기나 똑같다. 따라서, 경험을 많이 쌓아서 반전 증폭기와 비 반전 증폭기의 적절한 사용법을 찾아내시길 바란다. 위상 반전 여부로 증폭기 결선 형태를 결정짓기도 하니 경험을 많이 쌓아야 하겠다.

6. Instrumentation Amplifier (정밀 기기용, 계측용 증폭기)

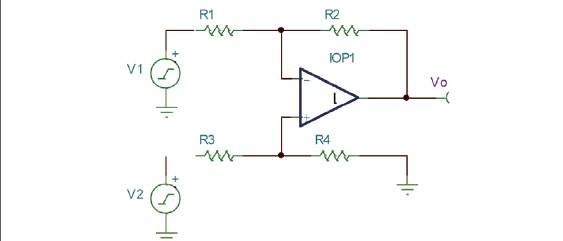

5절에서는 부하의 영향을 두루 살펴보았다. 741 Op Amp.의 입력 임피던스가 2M옴이고 출력 임피던스가 75옴이라는 것도 알았다. 이 정도 수준의 입출력 임피던스가 정밀/정확 계측 용도로 충분할까? 자고로 계측은 정확하고 정밀해야 한다. 정확하다는 기술용어와 정밀하다라는 기술용어는 ‘고정밀 계측’이라는 마케팅 용어에 모두 포함되어 있는데, 실상을 구분할 수 있어야 한다. 이런 식이다. 조준 사격을 했는데, 매우 우수한 탄착군은 형성되었지만 표적 중앙에서는 많이 벗어났다고 한다면, 정밀했지만 정확하지는 못한 것이다. 영점 조정을 하던지 해서 탄착군이 표적 중앙에 몰리도록 해야 한다. 고정확/고정밀 계측을 위해서 그림 4-3의 차분 증폭기를 사용한다고 해보자. 어떤 문제가 야기될까? 그림 4-3을 그림 6-1에 새로 그렸다.

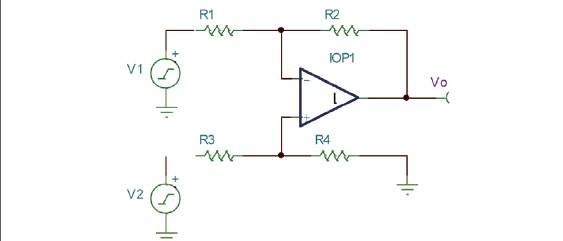

그림 6-1. 차분 증폭기 그림 6-1의 차분 증폭기 회로가 계측 용도로 사용된다고 해보자. V1신호가 R1을 거쳐 Op Amp.의 음의 입력단으로 전달되고 있다. V1에서 바라본 입력 임피던스는 R1 이기에, R1이 충분히 크지 않으면 심각한 Loading Effect를 겪을 수 있다. 그렇다고, R1을 키우자니 이득을 동일하게 유지하기 위해서는 R2도 커져야 하는데 한계가 있다. 너무 큰 R은 부정확하기도 하지만, 열 잡음도 커진다. 저항에서의 열 잡음은 저항 값의 제곱근에 비례한다. 게다가 증폭회로가 불안정해질 수 있다. 어떻게하면 좋을까? 안타깝지만 돈 좀 더 쓰자. 이럴 때, 아날로그 버퍼가 이용된다. 그림 6-2 회로처럼 꾸며보자. 신호원에다가 아날로그 버퍼를 다 달았다.

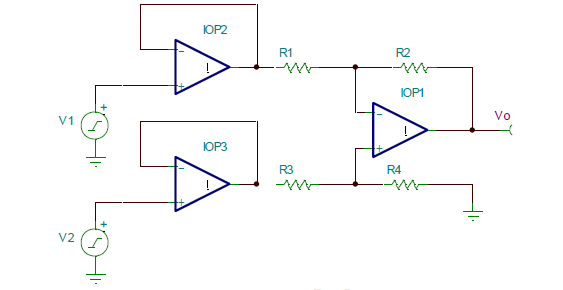

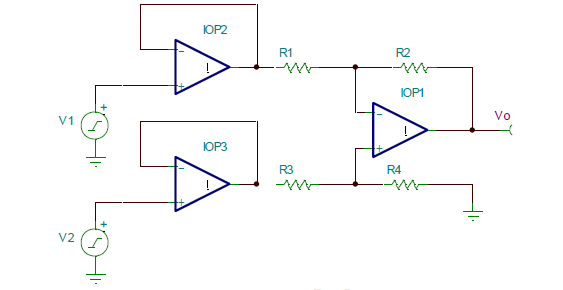

그림 6-2. 아날로그 버퍼를 추가한 차분 증폭기 Op Amp.가 무려 세 개나 쓰였다. 신호원에 아날로그 버퍼가 사용되다보니, 부하효과에 대한 고민은 이제 끝이다. 대체로 고정밀/고정확 시스템은 고가이면서 원가에 큰 부담을 갖지 않으니, 정밀/정확만 하다면 그림 6-2 회로처럼 3개의 Op Amp.로 하나의 Op Amp.를 대체한들 큰 부담이 되랴? 문제는 오히려 기판 면적을 많이 차지한다는 점이나, 생산 공수가 많이 든다는 점 등이다. 그래서, 반도체 회사들이 이런 요구를 해소시켜 상품화한 것이 바로 Instrumentation Amplifier다. 제품 카테고리가 형성될 정도로 인기있는 분야이면서 반도체 회사 입장에서는 고부가가치 분야이다. 그림 6-2회로에서 V2 신호원 쪽에 삽입된 아날로그 버퍼는 생략할 수도 있다. 이 경우는 Op Amp. 2개로 Instrumentation Amplifier를 구현한 것인데, 요즘은 거의 3개의 Op Amp.로 Instrumentation Amplifier를 구현한다. 대역폭도 그다지 넓지 않으면서도, 싸지 않다는 단점이 있다. 본격적으로 파고들어보자. 실제 부품을 예로 들어보겠다.

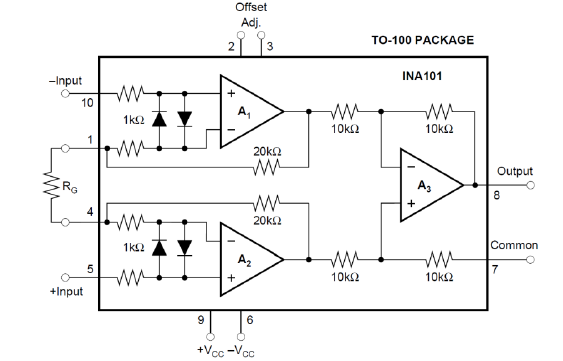

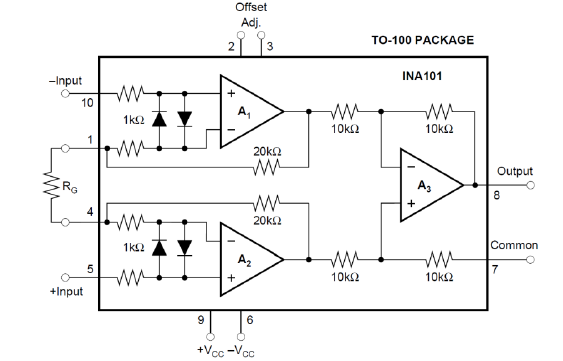

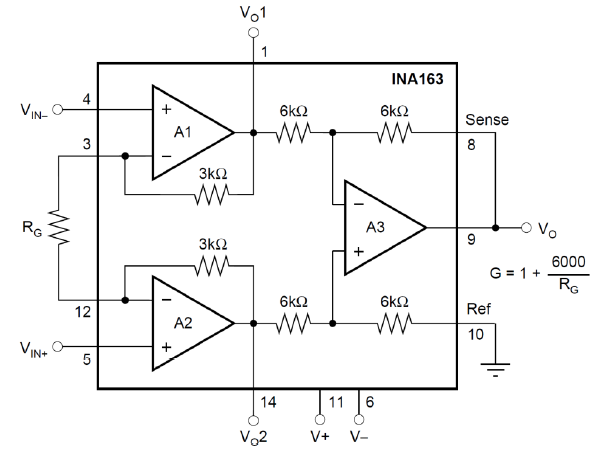

INA101이라는 부품이 있다. 서구에서 101이라는 숫자를 시작에 많이 쓴다. INA101은 Burr-Brown사가 만든 자사 최초의 Instrumentation Amplifier다. 그래서 101을 붙였다. Burr Brown사 제품은 명품으로 불리울 만큼 성능이 뛰어난 편이다. 지금은 Texas Instruments에 합병되어서 TI 제품으로 나온다. 그림 6-3은 INA101의 내부 구조를 보여준다. 짐작들 하셨겠지만, INA는 INstrumentation Amplifier의 앞머리 글자로 조합해 만든 것이다.

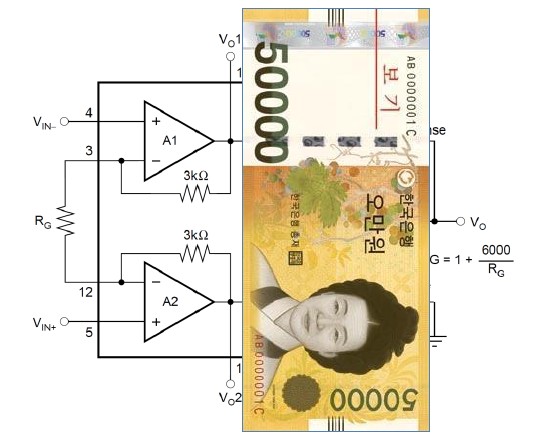

그림 6-3. INA101 내부 그림 6-3을 보면 Op Amp. 세 개의 존재를 확인할 수 있다.

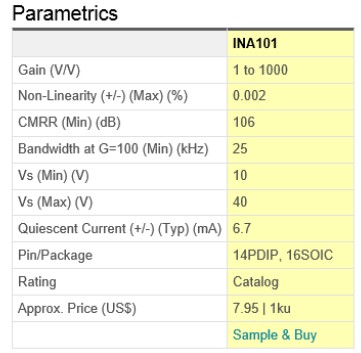

이 Op Amp.의 주요 특징을 ti.com의 제품 페이지에서 발췌해 그림 6-4에 옮겨두었다. 한번 음미해보자.

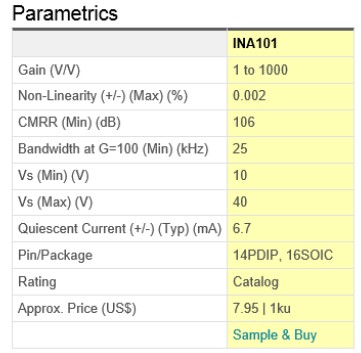

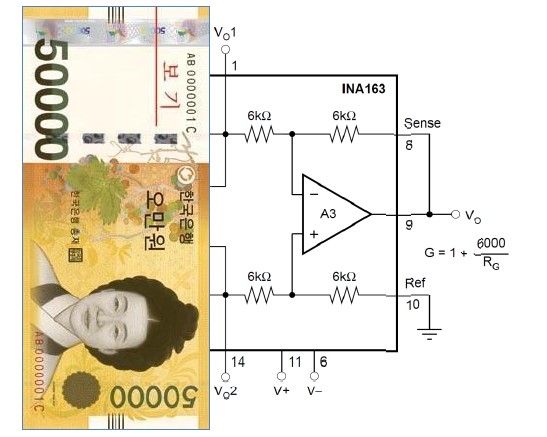

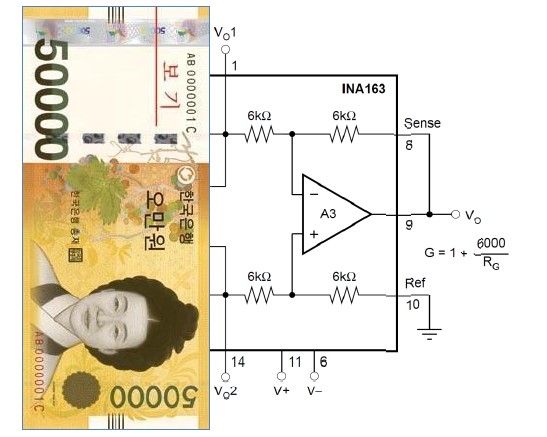

그림 6-4. INA101 제품 특징 이득을 최고 1천배까지 설정할 수 있다고 나와있다. 참고로, Instrumentation Amplifier의 이득 설정은 무지하게 쉽다. 그림 6-3을 보시라. RG만 유독 칩 바깥에 나와있지 아니한가! 그렇다. RG의 G는 게인을 뜻하는 것으로 게인 조절용 저항을 개발자가 적절히 선택해서 달아주세요 라는 의미이다. 비선형도가 매우 낮고, CMRR이 무려 106dB나 된다. 계측용으로 쓰이다보니 안타깝게도 대역폭(Bandwidth)은 그다지 크질 못하다. 전류 소비는 좀 많은 편이고, 가격이 1천개 기준으로 개당 7.95불이다. 웬만한 마이크로프로세서보다 더 비싸다. 산 조상님이라 그렇다. 새로 나온 Instrumentation Amplifier들은 많이 저렴해졌다. 좀 싼 것을 알아보자. ti.com에서 Amplifier and Linear 페이지로 들어가면 Instrumentation Amplifier 카테고리를 찾을 수 있다. 글쓰는 현재 43종이 등재되어있다. Difference Amplifier 제품군도 INA로 시작하는 것들이 있는데, 이 부분은 조금 아쉽다. 절대로 헷갈려서는 안된다. Difference Amplifier 제품군은 하나의 Op Amp.로 이뤄져 있다. 암튼, INA101은 너무 비싸다. TINA 라이브러리가 있는 제품 중에 값싼 제품으로 INA332가 검색된다. 1천개 기준으로 0.54불. 이 정도면 성능만 뒷받침된다면 돈 쓸 용의가 충분히 있을 법 하다고 본다. 그런데, 내부구조가 조금 이상하다. 처음 배우시는 분들에게 부적합해서 탈락. 그림 6-2회로와 같은 정석적인 형태를 취하면서, 4절에서 설명을 미뤘던, Sense와 Reference단자까지 함께 설명할 수 있는 INA163을 골랐다. 1천개 기준으로 2.9불이라 싸지는 않다. 내부 구조는 다음과 같다.

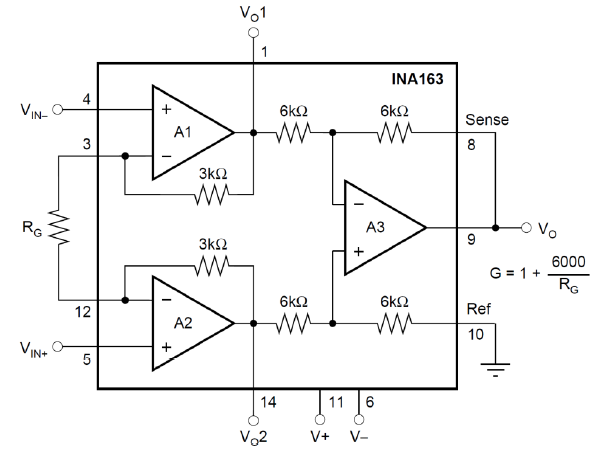

그림 6-5. INA163 내부 구조. 그림 6-2와 비교해보시라. 전형적인 Instrumentation Amp. 라는 것을 확인할 수 있을 것이다. 제품 특징을 보니, 1/f 노이즈가 1nV/√Hz@1KHz일 정도로 매우 작다. 대단하다. T.H.D(Total Harmonic Distortion) 수준도 엄청나게 낮다. T.H.D+N(Noise) 이 0.002%@1KHz, G=100 이다. 무슨 말인고 하니, 1KHz 정현파를 100배 증폭시켜서 얻은 결과의 스펙트럼을 분석해보면, 고조파와 노이즈 합이 0.002%에 불과하다라는 것이다. 이득이 100일 때, 대역폭은 800 KHz 나 된다. Instrumentation Amp. 치고는 상당히 큰 편이다. CMRR은 100dB 이상이나 된다. CMRR의 주파수 특성도 좋다. CMRR 그래프를 보니, 이득을 100배로 설정했을 때, 10KHz 에서 CMRR이 약 95dB 수준이다. Bravo! 돈 값 하는 듯.

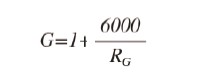

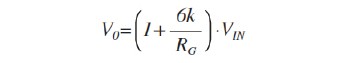

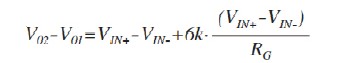

그림 6-5에서 부분을 한번 봐주시라. 바로 그 밑에 이득 공식이 나와있다. 이 칩의 이득 공식은

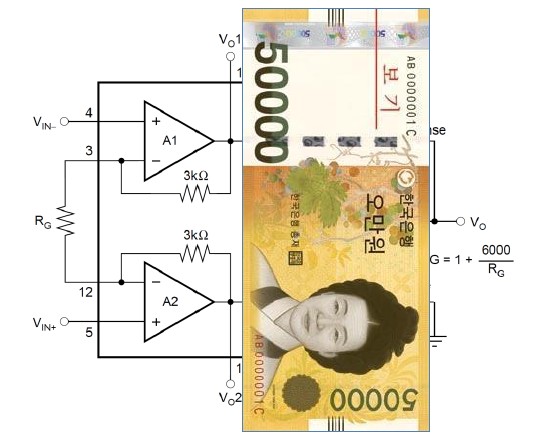

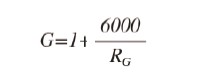

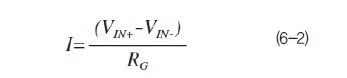

이다. 예를 들어, 601배의 이득을 원한다면, 매우 정밀/정확한 저항으로 10옴을 RG에 달면 된다. 이처럼 대부분의 Instrumentation Amp.는 제조업체가 이득 공식을 제품 설명서에서 명시하여 배포하고 있어서 사용하기가 한결 더 편하다. 돈을 좀 쓰니 이런 대접을 다 해준다. 하지만, 진짜 이 공식이 맞는지 한번 쯤은 확인해봐야 안되겠는가? 이번 기회에 한 번 해보자. 어떻게 풀어 낼 수 있을까? 잘 보면, 지금껏 배웠던 내용들이 눈에 쏙 들어올 것이다. 잘 안보이면 주위에 혹시 담배 갑이 있으면 아래 그림처럼 V01와 V02 죄측 영역을 가려보기 바란다. 담배 갑이 없으면 지폐라도 꺼내서 그림 6-6처럼 가려보자.

그림 6-6. 일부를 가린 Instrumentation Amp. 보이는가? 이전 호 4절에서 배웠던 차분 증폭기가 보인다. 차분 증폭기 풀이 법을 잘 모르겠으면 이전 호 4절을 다시 한번 읽어보자. 그리고, 그림 6-6을 보고 다시 한번 풀어보자. 저항이 모두 6K옴이니, V01와 V02와 V0의 관계식은 다음과 같다.

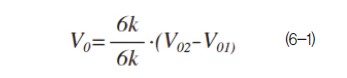

여기까지 구하신 분들은 지폐를 살짝 오른쪽으로 옮겨서 그림 6-7처럼 가려보자.

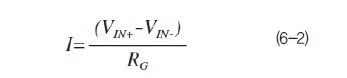

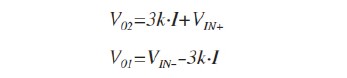

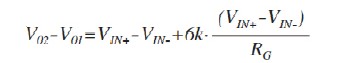

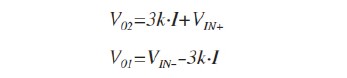

그림 6-7. 다른 부분을 가린 Instrumentation Amp. 이것 참! RG때문에 조금 복잡 미묘해진 듯 하다. 회로가 좀 복잡 미묘하다 싶을 때에는 조상님을 찾지 말고, 키르히호프(Kirchhoff) 할아버지를 떠올리자. RG에 흐르는 전류는 얼마인가? RG를 따라 위로 흐르는 전류는 I라 하자. 그렇다면,

이다. 이 전류가 A2증폭기의 궤환 경로에 있는 3k 옴 저항에도 흐르고, A1 증폭기의 궤환 경로에 있는 3k 옴 저항에도 흐른다. 그렇다면, 각각의 저항에서 발생하는 전압 강하를 더하거나 빼거나 하면,

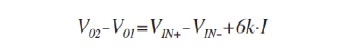

가 된다. 위 두 수식을 빼면,

가 된다. 여기에 (6-2) 수식을 대입하면,

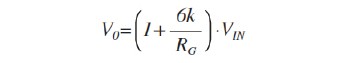

이 된다. 위 수식에서, VIN+-VIN-=VIN으로 바꾼 후, (6-1) 수식에 대입해보자. 그러면,

이 도출된다. 비싼 증폭기라 제품 설명서에 이득 공식이 나와있기는 하지만, 한번 쯤은 이득 관계를 직접 규명을 해봐야, Op Amp. 좀 써봤네! 라고 말할 수 있지 않을까?

7. Op Amp.의 Sense 핀과 Ref. 핀의 사용법

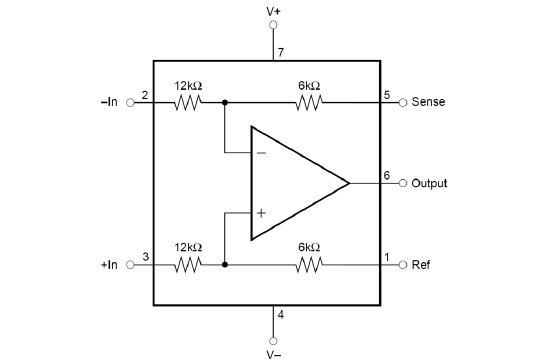

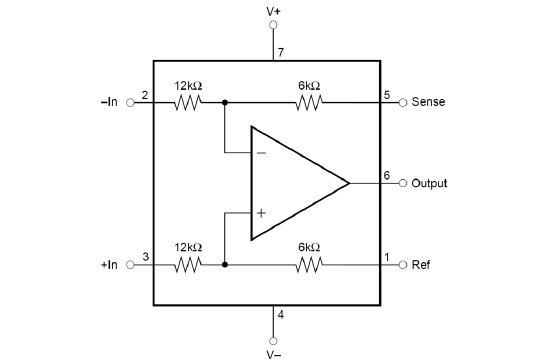

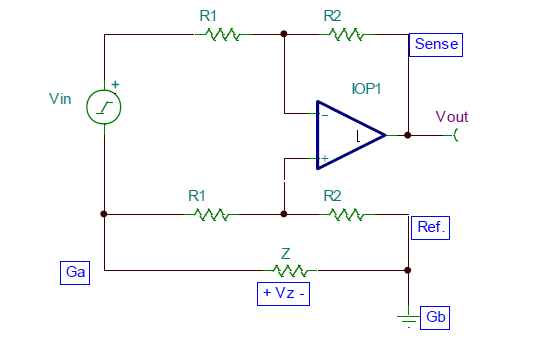

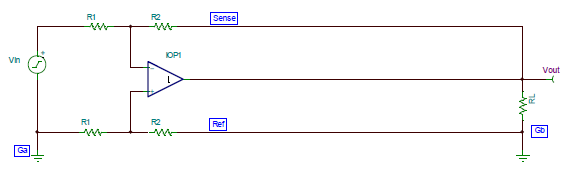

일부 Op Amp. 중에는 Sense와 Ref. 핀을 가지고 있는 제품들이 있다. 앞서 4절에서 살펴본 INA157과 같은 차분(Difference) 증폭기에도 이 핀들이 있고, 6절에서 배운 INA163과 같은 Instrumentation Amplifier에도 이 핀이 있다. 어떤 용도로 쓰일까? 다음은 4.4절에서도 본 INA157 내부 구조도이다.

그림 7-1. INA157 6절에서 다뤘던 INA163의 마지막 Op Amp. 역시 그림 7-1과 같은 구조이기에 그림 7-1로 Sense 핀과 Ref. 핀 용도와 사용법을 설명하면 부족함이 없겠다. 먼저 그림 7-1에서 Sense 핀을 보도록 하자. 이 핀이 만약에 개방(Open) 되어 있다면, 궤환(Feedback) 경로가 구성되지 않기에 증폭기로 사용이 어렵겠다. 따라서, Sense 핀은 어떤 식으로든 출력 단에 접속되어야 한다. Ref. 핀 처리 방법은 여러 가지가 있을 수 있겠는데, 만약 차분증폭기가 필요하다면 Ref 핀은 접지에 접속되어야 한다. 여기까지는 지금까지 배웠던 내용인데, 하필이면 왜 Sense 라는 말과 Ref. 라는 말을 이 핀에다가 붙였을까? 이유가 있을 테니, 캐내어 보자.

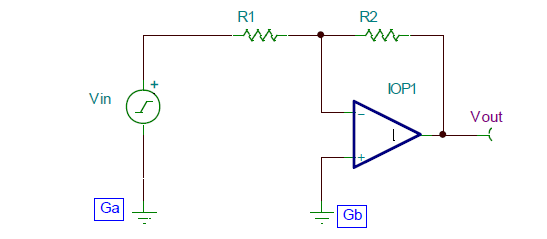

먼저, Ref. 핀을 이용한 불완전 접지 해소법에 대해서 살펴보자. 구현하고자 하는 시스템 규모가, 큰 공간이나 면적을 차지한다면 접지에 문제가 발생할 수 있다. 결과적으로 접지가 0V가 아닌 상황이 벌어질 수 있는 데, 이를 불완전 접지라 한다. 불완전 접지를 그림 7-2와 같이 모델링 해 볼 수 있겠다.

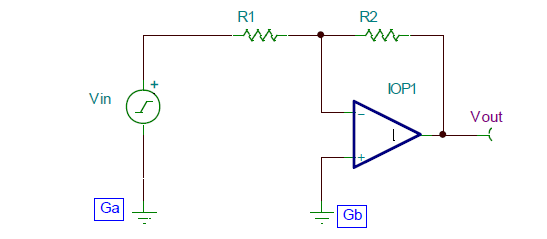

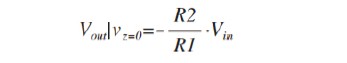

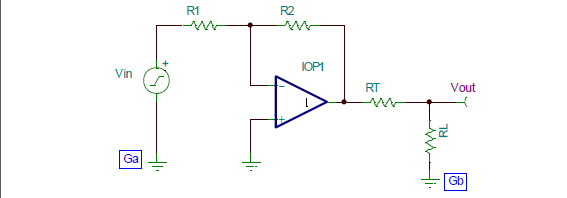

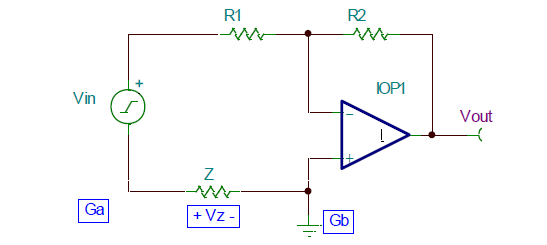

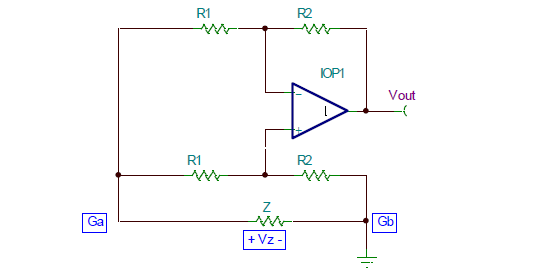

그림 7-2. 모델링한 불완전 접지 : Ga와 Gb의 전위가 다름 그림 7-2의 회로를 보면, 신호원의 (-)단자와 Op Amp.의 (+) 입력단이 동일한 접지 기호에 연결되어 있는 것을 확인할 수 있다. 그런데, 물리적으로 두 접지간의 거리가 제법 멀어지면, 접지간에 저항 값이라던지, 기생 커패시턴스, 인덕턴스 성분등으로 인하여, 전위차가 발생하는 경우가 종종 생긴다. 제법 멀리 떨어진 센서 등과 결속할 때 이런 문제들이 발생한다. 등가모델로 표현하자면 다음과 같이 표현할 수 있다. Op Amp. 쪽 접지 Gb를 주 접지로 간주하고, Gb 접지와 Ga 접지 사이의 전압 강하를 Vz라 하면, 그림 7-3과 같은 등가 모델로 불완전 접지를 표현할 수 있겠다.

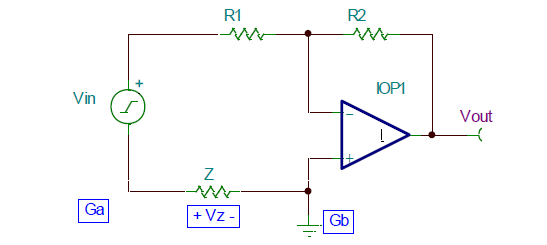

그림 7-3. 불완전 접지 등가 회로 더 이상 Ga에는 접지 기호가 없다. 임피던스 성분 Z 로 주 접지Gb와 연결된 형태다. 문제는 Z의 정체를 모른다는 것이고, 시변(Time varying)할 수 도 있다는 점이다. Vz를 고려한 입출력 관계식은 어떻게 되는가? 중첩의 원리를 적용하여서 구해보자.

수식을 통해서 알 수 있듯이, 불완전 접지로 인해서 발생한 VZ까지도 증폭이 된다. 큰일이다. 접지간 거리를 최소화한다던지, 하더라도 Vz를 완전히 없애기는 불가능하다. 어떻게 할까? 그래서, Ref. 핀이 만들어졌다. 그림 7-4를 보자.

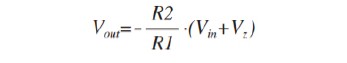

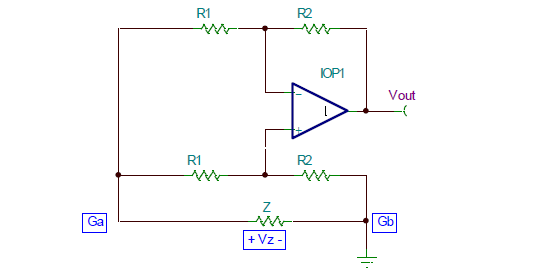

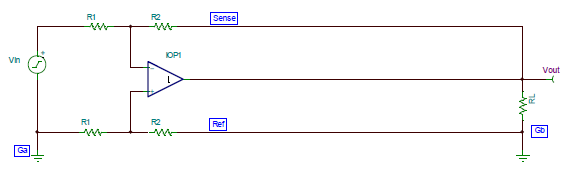

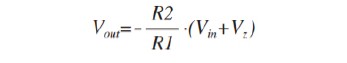

그림 7-4. Ref. 핀을 이용한 불완전 접지 해소법 그림 7-3 회로에는 일반적인 Op Amp.가 사용되었다. 그림 7-4 회로에서는 INA157같은 Ref. 핀을 가진 차분 증폭기가 사용되었다. Sense 핀은 아직 안 배웠으니 일단 출력단에 바로 물려 놓자. Ref. 핀은 Gb 접지에 연결하자. 접지간 전위차를 Vz로 표시했다. 주의할 것이 하나있다. 그림 7-4의 R1, R2 저항은 반도체 패키지 내부의 저항이기에 실제 회로는 전혀 복잡하지 않다는 점을 주의해야 한다. 그림 7-4 회로의 전달함수를 구해보면 Vz가 어떻게 제거되는지를 정확히 그리고 쉽게 이해할 수 있다. 중첩의 원리를 적용하여, Vin에 대한 응답을 구해보자. Vz를 0으로 만들어야 한다.

이다. 이제, Vz에 의한 응답을 구해보자. Vin 영향을 0으로 만들어야 한다. 즉, 단락(short)시켜야 한다. 그러면 회로가 어떻게 되는가?

그림 7-5. Vz에 의한 출력을 구하는 회로 Vz가 위쪽 R1을 거쳐서 Op Amp.의 (-) 입력단으로 전달된다. 동시에, 아래쪽 R1을 거쳐서 Op Amp.의 (+) 입력단으로도 전달된다. Op Amp. 두 입력단 전위는 동일하다. 그렇다면 차분 증폭기의 출력은 0이다. 따라서, 두 결과를 중첩하여 응답을 구하면,

이다. 어떤가? 간단히 설명하자면, Op Amp. 양단 입력 차만 증폭하는 차분 증폭기의 성질과 Ref. 핀을 이용하여, 불완전 접지로 발생하는 전압을 제거하는 것이다. Ref. 핀을 잘 활용하면, 불완전 접지로 인해서 야기된 전압을 차분 증폭기 양 입력단에 똑같이 전달하기에 차분 과정에서 없어져 버리는 것이다.

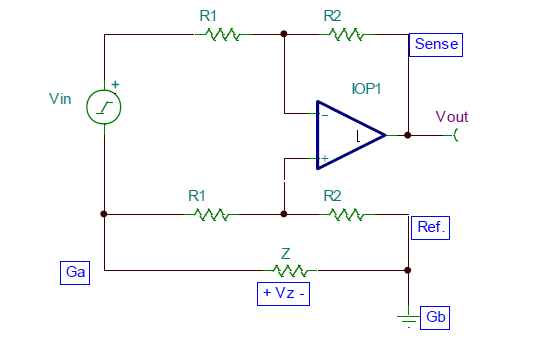

이제는 Sense 핀의 활용방법을 알아보자. 그림 7-6을 보자. RL이 멀리 떨어져 있다. 책이 좀 더 컸으면 실감나도록 멀리 그렸을 것인데, 좀 아쉽지만, 많이 멀다고 해보자. 멀리 떨어진 장치 등을 구동하는 예가 되겠다.

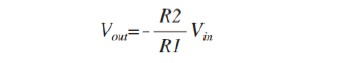

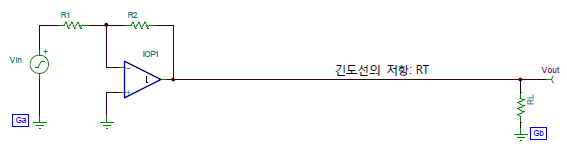

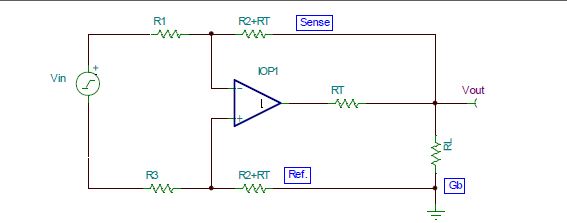

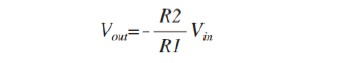

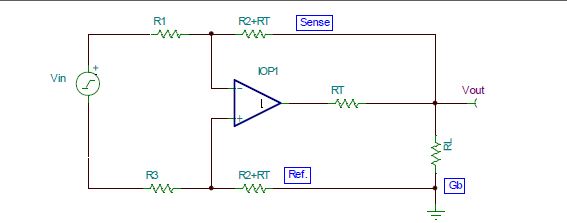

그림 7-6. 멀리 떨어진 부하를 구동하는 예 그림 7-6에서 R1과 R2가 각각 1K옴 및 10K옴이라면, RT를 고려하지 않은 이득은 10배이다. 이제 RT를 고려해보자. 도선이 제법 길어서 RT가 100옴이나 된다고 해보자. 그리고, RL 또한 100옴이라고 한다면, 그림 7-6 회로 전체의 이득은 5배에 불과하다. 즉, 도선에 의해서 Loading Effect가 심각하게 발생한 것이다. 그림 7-7에 도선의 저항까지 고려한 등가회로를 그려놓았다.

그림 7-7. 도선 저항을 RT로 모델링한 등가회로 그림 7-7 회로가 애초 계획했던 시스템 전체 이득 10배를 달성하려면 R2를 20K옴으로 바꿔주면 되겠는데, 문제는 도선의 저항이 얼마인지 정확히 모른다거나 시간에 따라 변한다거나 한다면 어떻게 해야 할까? 그렇다고 포기할 수는 없는 노릇이다. 이럴 때, Sense 핀이 필요하다.

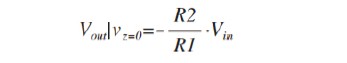

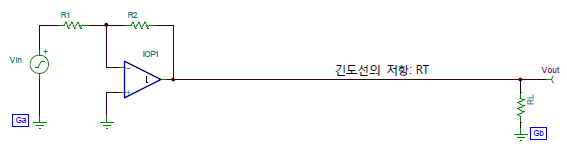

그림 7-6 회로를 그림 7-8 회로처럼 꾸며보자. RT에 의해서 출력 저하가 발생한다는 점, 즉, Loading Effect가 발생한다는 점 잘 아시리라 본다. 원치 않는 바다. 어떻게 극복 할 수 있을까? 저항 값이 작은 도선을 사용하는 것은 비현실적일 수도 있기에, Sense 핀을 이용하여 이를 극복한다. 다음 회로를 보자.

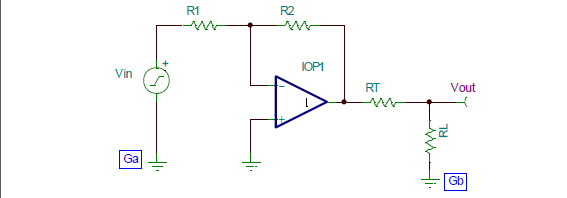

그림 7-8. Sense 핀을 이용한 무손실 장거리 부하 구동 예 그림 7-8 회로는 Sense 핀의 의미가 확 다가올 법한 회로다. 목표 지점의 전압을 감지하여 피드백 시키는 역할을 Sense핀이 한다. 전체적으로는 차분 증폭기를 꾸며야 하기에, Sense 핀으로부터 Vout 지점까지, 그리고, Ref. 핀부터 부하의 접지 지점까지는, 그림 7-8처럼 동일한 도선으로, 똑같은 길이로, 회로를 구현해야 한다. 이렇게 되면, R2는 R2 + RT가 되어 우리가 흔히 보는 차분 증폭기가 된다. 그림 7-9 회로가 등가회로다.

그림 7-9. 그림 7-8의 등가회로 그림 7-9와 같은 회로가 형성이 되면, 도선의 저항은 Op Amp. 출력 저항으로 바뀌게 된다. 따라서, 원거리에 대한 출력 전압 저하 우려도 싹 가시게 된다. 반대로, 도선의 저항만큼 R2가 커진 형국이기에 전체적인 이득은 조금 커진다. 필요하다면, Ref. 핀을 부하 쪽 접지가 아닌, 가까운 쪽 접지에 물려도 된다.

Ref. 핀의 또 다른 사용 예가 있다. Ref. 핀에 가변 저항을 달아 조절하면 출력 신호의 오프셋(Offset) 을 조정할 수 있다. 하지만, 고 신뢰성 제품이나 양산 제품에 가변 저항을 사용하는 것을 무척이나 좋아하지 않는 필자이기에 내용에서 빼버렸다. 궁금하신 분은 TINA로 차분 증폭기의 + 입력단에 연결된 R2 저항을 Control Object로 설정하여 값을 바꿔가며 시뮬레이션 해보시기 바란다. 출력 오프셋이 달라짐을 확인할 수 있을 것이다.

다음 시간에는 마지막으로 8. 단전원(Single Power Supply) 조건에서 Op Amp. 구동과

9. Fully Differential Op Amp. (FDA) 대하여 살펴보도록 하겠습니다.

|