|

아날로그필터와 OPAMP

Op Amp. 사용설명서 PART 1

글 | (주)싱크웍스 백종철

본 글은 “아날로그필터와OPAMP, ㈜싱크웍스 출판사, 백종철” 책자에서 자칫 많은 개발자들이 그 중요성을 간과 하기 쉽지만 실전에서 꼭 필요한 OPAMP에 대한 내용을 디바이스마트 매거진 독자들을 위해 발췌하여 수록하였습니다. |

목차

1. Op Amp. 실제 부품의 이해와 핀 설명

2. Op Amp.의 전원 공급과 전류의 흐름

3. Rail to Rail Input Output(RRIO) 방식의 장점

4. CMRR과 PSRR

5. Loading Effect (부하의 영향)

6. �Instrumentation Amplifier

(정밀 기기용, 계측용 증폭기)

7. Op Amp.의 Sense 핀과 Ref. 핀의 사용법

8. �단전원(Single Power Supply) 조건에서

Op Amp. 구동

9. Fully Differential Op Amp. (FDA)

이 글에서는 능동 필터의 핵심 소자로 사용되는 Op Amp.에 대한 내용을 다룬다. 쓰다 보니 양이 너무 많아져서, 취사 선택을 해야만 했다. 첫번째 기준으로는 FilterPro 사용에 있어서 부족함이 없도록. 둘째는, 현장에서 흔히 놓치는 Op Amp.의 중요한 성질들을 확실히 다루자 라는 것이었다. 아울러 실제 부품을 사용했을 때 발생 가능한 현상들을 TINA를 통해서 확인하는 과정을 곳곳에 배치했기에, 현 업무에 직접적으로 도움이 될 것이다. 마지막으로는, 최근 들어 주목받고 있는 FDA(Fully Differential op Amp.)를 다뤄봤다. 막상 별다를 바가 없다는 것을 이해하실 수 있을 것이다.

1. Op Amp. 실제 부품의 이해와 핀 설명

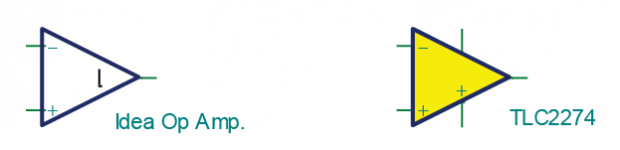

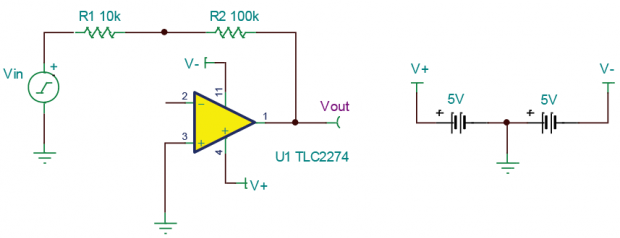

그림 1-1은 TINA에서 사용되고 있는 이상적인 Op Amp. (연산 증폭기)와 실제 Op Amp.의 핀을 보여 주고 있는데 일반적으로 이렇게들 사용하고 있다.

그림 1-1. TINA에서의 Op Amp. 라이브러리 좌. 이상적인 Op Amp. 우. 실제 부품 Ideal Op Amp의 경우, DC 전원 관련 핀을 생략하고 있기에 통상 세 개의 핀으로 Op Amp.를 구성한다. 우측의 TLC2274는 저전압용 Op Amp.로 만만하게 쓰이는 제품이며 Texas Instruments 사에서 공급한다. 전원 공급핀이 추가되어 핀이 총 다섯개다. 일반적인 경우다. 어떤 Op Amp. 들은 단일 Op Amp. 이면서도 7핀이나 9핀까지도 가지고 있는 것들도 있다. 이런 것들은 차츰 알아보기로 하고 우선은 5핀 표준 부품을 가지고 설명을 시작해보겠다. 먼저 Op Amp.를 이용할 때 가장 많이 쓰는 증폭 회로를 살펴보면서 핀에 담겨 있는 심오한 내용을 이해해 보도록 하자.

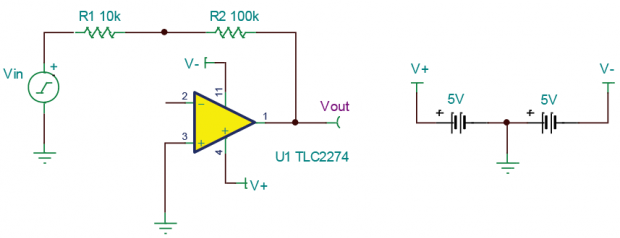

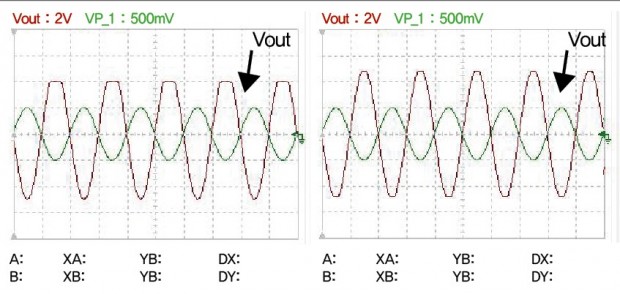

그림 1-2. TLC2274로 꾸민 반전증폭기 그림 1-2의 회로는 TLC2274 Op Amp.로 입력신호를 10배 증폭하면서, 출력신호의 위상이 입력신호와 180도 차이나는 반전 증폭기를 만든 것이다. 10배를 증폭한다면, Peak To Peak 전압, 즉, Vpp가 100V 인 정현파를 인가하면, 1,000Vpp 정현파가 만들어진다. 맞나? 일단은 너무 큰 것 같다. 앞서 TLC2274는 저전압용 Op Amp.라고 했는데, 100Vpp와 1000Vpp는 너무 큰 것 같다. 눈치 빠르신 분은 그림 1-2 회로에서 TLC2274에 공급된 전원이 +/-5V 이기에 출력 전압이 이 범위를 벗어날 수 없음을 잘 아실 것이다. 하지만, Op Amp.를 낯설어 하시는 분들도 계실 것이다. 그래서, TLC2274의 주요 규격부터 살펴보았다. TLC2274의 제품 설명서를 구하기 위해서 www.ti.com 을 방문 후 검색했다. 해당 제품 페이지를 찾아, 상단부를 캡쳐하여 그림 1-3에 옮겼다.

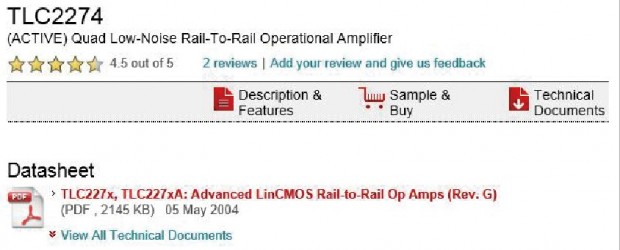

그림 1-3. TLC2274 제품 웹 페이지 TLC2274 라는 부품명이 선두에 보이고, 바로 아래줄에 ‘(Active)’라는 말로 현재 생산중임을 알려주고 있다. 이어서 ‘Quad Low-Noise Rail-to-Rail Operational Amplifier’ 라는 문구가 보이는데 제품의 주요특징을 압축해서 잘 알려주고 있다. Quad라는 말은 한 패키지에 Op Amp.가 4개 들어있다는 얘기다. 그렇다면, 이 패키지의 총 핀 수는? Op Amp.당 5개가 필요하니, 총 20개가 될 터인데, 전원 핀을 공유한다면 14핀이면 해결 가능하다. 실제 14핀 SOIC, 14핀 TSSOP, 14핀 PDIP, 14핀 SO 패키지등으로 공급되고 있다. ‘Low Noise’ 라는 말은 받아들이기는 쉬우나, 정말로 얼마만큼 Low Noise인지는 판단하기가 무척 어렵고 그 안에 녹아든 기술 또한 이해하기가 만만찮다. 이 절에서는 부품을 사용하는 입장에서 Low Noise 여부를 가늠할 수 있는 지표들을 설명하도록 하겠다. 이어서 ‘Rail-to-Rail’ 이라는 용어가 나왔는데, 중요한 용어다. 일단은 저전압용 시스템에 적절한 전원 회로를 탑재하여, 낮은 전압에서 최대한 출력 신호 진동을 보장한 방식이라고만 이해해두자. 3 절에서 정밀하게 다루고 있으니, 조금만 기다려 주시기 바란다.

이어서, 고객들 평점과 평, 그리고 몇몇 아이콘들이 있고, 바로 밑에 Datasheet, 즉, 제품 설명서가 보이면서, 받아 보실 수 있도록 링크를 걸어 놓았다. 제품 설명서 이름은 ‘TLC227x, TLC227xA : Advanced LinCMOS Rail-to-Rail Op Amps (Rev.G)’ 라고 되어있다. 함축적 설명이다. 풀이하자면, TLC227x에서 x는 계열을 의미하는 것으로 이 계열에는 TLC2272와 TLC2274가 있다. 2272는 한 패키지에 Op Amp.가 2개 있는 것을 말한다. 이 패키지의 핀은 몇 개 일까? 그렇다. 전원을 공유하다 보니 8개이다. ‘Advanced LinCMOS’는 Texas Instruments사가 자랑하는 아날로그 반도체 제조 공정 중에 하나를 의미한다.

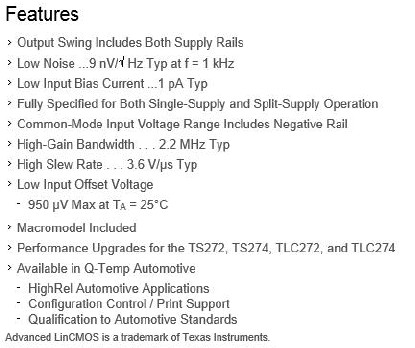

이어서 Description 항목이 나온다. 여기에서는, 주요 특징을 몇몇 문단에 걸쳐 설명하는데 사실 온갖 자랑이다. 여기에 혹해서는 안되고, 정말로 제대로 된 자랑인지는 제품 설명서를 봐야 하는데, 주목해야 할 부분은 ‘CMOS’ 라는 용어다. CMOS는 Complementary Metal Oxide Semiconductor의 앞머리 글자로 주로 상보성 금속 산화물 반도체 라고 옮기는데 필자도 이해가 어렵다. 갸우뚱! 무엇보다도 한자로 옮긴 말에는 중요한 정보 하나가 누락되어 있다. CMOS FET(Field Effect Transistor)로 그냥 옮겨 쓰는 것이 더 나을 듯 하다. 즉, 이 Op Amp.는 N형 MOS FET 와 P 형 MOS FET로 구성된 FET형 Op Amp.다. Op Amp는 BJT로 구성되기도 하고, FET로 구성되기도 하고, BiCMOS (BJT+CMOS)로 만들어지기도 한다. 초기의 Op Amp.는 BJT로 만들어 졌는데, 최근 들어서 CMOS로 된 Op Amp.가 널리 보급되고 있다. 각각의 장단점이 있는데, 범용으로 쓰기에는 어떤 것을 써도 큰 차이 없다. 반도체 회사들이 알아서 잘 만들고 있다. 다만, CMOS 공정이 BJT 공정보다 상당히 간단한 편이고, 대부분의 디지털 회로들이 CMOS 공정으로 만들어지기에 Op Amp. 도 CMOS로 만들어가는 추세다. 일반적으로는, BJT로 구현된 Op Amp.가 FET로 구현된 Op Amp보다 전반적인 성능이 우수하다고 평가되지만, FET로 구현된 Op Amp.가 우세한 부분도 더러 있다. 바로 입력 임피던스 항목이 그 중 하나인데, 왜냐면, FET의 경우, 입력 단자로 쓰이는 Gate단과 전류가 흐르는 Source-Drain간의 채널 사이가 절연이기 때문이다. 실제로 TLC2274의 입력 임피던스는 10^12 옴 = 100만메가 옴 = 1천기가 옴 = 1테라 옴이다. 무지하게 크다. 참고로 Op Amp.의 산 조상격인 uA741 Op Amp.의 입력 임피던스는 2M옴에 불과하지만, 작다고 할 수는 없는 편이다. 따라서, 특별한 경우가 아니라면, CMOS건 BJT건 구분없이 사용해도 된다. 중요한 것은 CMOS냐 BJT냐 하는 것보다는 세부 규격이다. 단, 5절에서 설명하는 Loading Effect 때문에 큰 입력 임피던스가 필요하다면 당연히 CMOS로 구현된 Op Amp.가 적합하다. 이어서 ‘Feature’ 부분이 보인다. Op Amp. 선택 시 먼저 이 부분을 자세히 살펴보고 궁합을 따져본 후 맞겠다 싶으면 제품 설명서를 탐독해야 한다.

그림 1-4. TLC2274의 주요 특징 먼저, Output Swing Includes Both Supply Rails 라는 항목이 나오는데, 앞서 언급한 Rail-to-Rail 특성을 말한다. 4.3절까지 보류 해 두자. 이어서, Low Noise 항목이 나온다. 9nV/ Hz라고 수치로 명시하고 있는데, 감이 잘 안 온다. 일단, 9nV라고 하니 무지하게 작은 것 같다. 단위가 좀 특이하다. 9nV/ Hz라니? 주로 전자 부품 자체에서 발생하는 Noise를 알려주는 지표이다. 다시보니, 1KHz에서 9nV Hz 라고 명시하고 있다. 이를 총칭해서 1/f 노이즈라고도 한다. 엄밀히 말하면, 1/fα 노이즈라고 한다. TLC2274 특징에서는 α=0.5인 경우인데, 이게 정수가 아니면, Fractal 현상을 보이기에 Fractal Noise 라고도 한다. α=1이면 Pink Noise, 혹은 Flicker Noise 라고도 한다. 741 Op Amp.는 이 값이 어느 정도될까 궁금하여 찾아보니 없다. 인터넷을 여기저기 뒤져보니 100nV Hz수준인 듯한데, 확실한 비교를 위해서 LM2902를 찾아봤다. 35nV Hz이다. 확실히 TLC2274가 작다. Low Noise다. 하지만, TLC2274가 LM2902보다 5배 넘게 비싸다는 것은 함정.

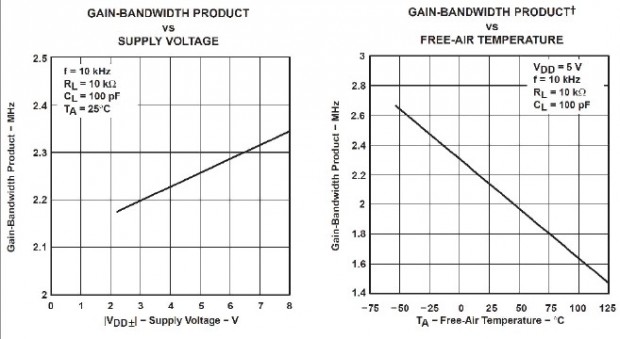

다음으로, Low Input Bias Current가 통상 1pA 라고 말한다. 이는 CMOS로 구현되었기에 가능한 수치다. 입력 임피던스가 1테라 옴이라서 가능한 수치다. 이어지는 두 항목은 Rail-to-Rail을 설명할 때 다루기로 하자. High Gain Bandwidth가 통상 2.2MHz 라고 한다. High Gain-Bandwidth라, 이런 용어는 없다. 아마 뒤에 말이 생략된 듯 하다. 복구하자면, High Gain-Bandwidth Product일 것이다. 실제 DataSheet를 살펴보면, Gain-Bandwidth Product 항목으로 +/-5V 전원으로 동작할 경우, 2.25MHz 라는 값이 나온다. 증폭기를 다룰 때 있어서 대역폭(Bandwidth)는 어느 주파수 신호까지 증폭할 수 있는지를 알려주는 매우 중요한 지표로, Gain-Bandwidth Product 항목은 증폭비 1배를 기준으로 할 때, 2.25MHz까지는 1배 증폭이 가능하다는 얘기다. 2배 증폭을 원한다면, 대역폭이 반으로 줄어든다. 10배 증폭을 원한다면, 225KHz 까지로 제한된다. 이게 그 유명한 ‘Gain-Bandwidth Product Rule’ 이다. 모든 증폭기는 이 규칙에 지배된다. 즉, 이득과 대역폭의 곱은 일정하다라는 규칙이다. 앞서 말한, 2.25MHz를 단일 이득 대역폭 주파수 (Unity gain bandwidth frequency)라고 말한다. 그런데 이 수치가 공급 전압에 따라 변하고, 온도에 따라 변한다는 점을 명심해야 된다. 그래서 제품 설명서에는 반드시 다음과 같은 그래프가 있으니 두 눈 부릅뜨고 유심히 읽어야 한다.

그림 1-5. TLC2274의 공급전압과 온도에 따른 Gain-Bandwidth Product 그래프 그림 1-5의 좌측 그래프는 공급 전압에 따른 그래프다. 그 차이가 그렇게 크지는 않지만, 공급 전압이 낮을수록, Gain-Bandwidth Product 수치는 낮아진다는 점에 주목해주시길 바란다. 우측은 온도에 따른 수치다. 2.25MHz 수치는 대략 0도에서 측정된 수치인 것이다. 주위 온도가 50도 정도 된다면 2MHz 이하로 떨어진다. 광대역 신호를 다루는 경우에는 정말로 주의해야 한다. 75도에서는 1.8MHz 에 불과하다는 점. 많이들 놓치는 부분이다. 그래서, 이 책에 특별히 실었다.

다음은, Slew Rate 항. 이 항은 Gain-Bandwidth Product 항과 밀접한 관계가 있다. Gain-Bandwidth Product 수치가 높을수록 Slew Rate는 높다. 단위가 의미하듯이, 1usec 동안에 출력이 통상 3.6V 상승할 수 있는 능력을 갖췄다는 얘기인데, 요즘은 수십V/usec의 Slew Rate을 가진 Op Amp.도 수두룩하다.

다음 항목으로 Low Input Offset Voltage 라는 항목이 나와 있는데, 25도 상온에서 950uV 라고 한다. 과연 적은 값일까? 단위를 달리 하면, 0.95mV다. 크게 느껴진다. Low 라니. 사기… 일단 Input Offset Voltage가 뭔지부터 알아야겠다. Op Amp.의 두 입력단, 즉, +/- 입력단을 저항이 0인 도선으로 연결했다면, 출력은 0 이어야 한다. 그런데 0V가 아니다. 심각하다. 출력을 0으로 만들기 위해서 별도의 DC 전압을 인가해보니 출력이 0이 되더라고 한다면, 추가한 전압을 Input Offset Voltage 라고 한다. 주된 원인은 Op Amp. 입력단 차동 증폭기에 쓰인 트랜지스터가 기하학적으로나, 도핑 농도적으로나 동일하지 않기 때문인데, 요즘은 정밀 제조 기술 덕에 이 값이 많이 줄어들었다. 따라서, 950uV는 결코 작은 값이 아니다. Texas Instruments사는 자사 제품군들 중에 Input Offset Voltage가 500uV이하인 것들을 Low Input Offset Voltage 제품군으로 구분하고 있다. Texas Instruments사의 OPA4727이라는 제품을 보면, TLC2274처럼 CMOS로 구현된 4개의 OP Amp.를 내장하고 있다. 가격은 TLC2274에 비해 1.8배쯤 되지만, Input Offset Voltage가 통상 15uV에 불과하다. 놀랍지 아니한가? 이 정도는 되어야 Low Offset Input Voltage라고 말할 수 있겠다. OPA 계열이 한 성능한다. 최근에 나온 제품일수록 Input Offset Voltage 값이 작다. 왜냐면 정밀생산 기술이 발전하고 있기 때문이다. OPA4727, 기억해둘 만한 부품이다. 적당한 가격에, Gain-Bandwidth Product가 20MHz나 되며, 입력 임피던스가 0.1테라 옴이며, 저전력이기 때문이다. HiFi 오디오에 더러 쓰이는 뛰어난 제품이기도 하다. 이어서 Macro-model Included라는 말은, TINA에서 사용할 수 있는 Spice 라이브러리가 제공되고 있다는 것을 의미한다. 다음 그림처럼 제품 페이지 우측상단에 링크되어 있다.

그림 1-6. TLC2274 의 개발자 지원 항목 TINA와 같은 시뮬레이션 프로그램용 라이브러리가 제공되고 있으며, 필터 디자인 소프트웨어도 지원하며, 이 Op Amp. 의 성능을 직접 평가해볼 수 있는 키트류도 제공하고 있다는 것을 알려주고 있다.

이어지는 항목은 ‘TS27x나 TLC27x 보다 개량된 제품이기에 이것들 말고, TLC227x를 사용하세요.’ 라는 말을 전하고 있다. 새로 나온 제품이 대체로 성능도 좋고, 가격도 싸다. 따라서, 신제품을 열심히 찾고 골라야 한다. 단, 일부 회사 제품의 경우, 제품 설명서에 나와있는 규격과 동떨어진 성능을 보이는 경우도 있기에 주의해야 한다. 반드시 평가를 해보고 사용해야 한다. 필자가 경험한 제품과 해당 회사들을 소상히 밝히고 싶기도 한데, 그 사이에 개선을 했었을 수도 있으니 참겠다. 몇 번의 평가 실험을 했는지 모른다. 분하다. 참고로 Texas Instruments사 제품에는 이런 경우가 없었다. 경험상으로는, 제품 설명서에 오실로스코프와 같은 계측기 측정 화면을 직접 캡쳐해서 제품 규격을 설명하는 경우, 좋은 결과를 보여주는 듯 하였다. 그만큼 자신있다는 의미인 듯. 참고하시길…

마지막은 여러가지 변형 제품들이 있음을 소개하는 문구들이다. 전장품 온도 규격(Q Temp.)을 만족하는 제품, Op Amp. 전원을 차단하는 핀이 있는 제품등이 있음을 알려주고 있다.

2. Op Amp.의 전원 공급과 전류의 흐름

다시 한번 짚고 넘어가자. 그림 1-1처럼, 실제 Op Amp. 부품은 다섯개 이상의 핀으로 구성되어 있다는 것을 기억하자. 그런데 몇 개의 핀이 있다고 한 들, 아무리 찾아봐도 접지 핀은 없다. 이게 무슨 말이냐 하면, 다섯개의 핀을 가지는 Op Amp. 라고 할 때, 다섯개 핀들 중에서 접지와 연결하는 핀은 존재하지 않는다 라는 것이다. 그림 1-2를 다시 가져와서 보자.

그림 2-1. 다시 보는 그림 1-2 그림 2-1 회로에서 Op Amp.를 잘 보시라. + 입력단 핀, – 입력단 핀, 출력단 핀, + 전원단 핀, 그리고, – 전원단 핀, 이렇게 다섯개 핀만 있다. Op Amp. 본체에는 접지와 연결하는 핀이 없다. 주의. 그림 2-1에서 + 입력단에 접지를 연결한 것은 + 입력단에 접지를 입력시킨 것. 즉, 0V를 + 입력단에 입력시킨 것임을 이해해야 한다. 이렇게 얘기할 수는 있다. Op Amp.를 단전원(Single Power Supply)용으로 사용할 경우, 예를 들어, +5V 만을 단독으로 사용할 경우, 그림 2-1 회로에서 Op Amp.의 V- 핀은 접지에 연결된다. 하지만, 이거는 V- 핀이 0V에 연결된 것이고, Op Amp. 자체에는 접지와 연결하는 핀이 없다라는 점을 명확히 이해해야 한다.

Op Amp.는 접지를 필요로 하지 않는가? 예를 들어, 그림 2-1 회로에 +/-5V를 공급했다고 하자. 접지는? 접지는 어디에? 일반적으로 대칭형 전원을 공급하게 되면, Op Amp. 내부에 0V가 생긴다. 이것을 가상(Virtual) 접지라 한다. 0V가 생성되는 이유는 Op Amp. 내부 회로가 대칭형으로 설계되었기 때문이다. 이 대칭성에 문제가 생기면 Input Offset Voltage가 생길 수도 있는 것이다. 하지만, 대칭 전원이 아니더라도 가상 접지 생성에는 문제가 없으니 안심하셔도 된다. 만약, V+ 가 3.3V에 연결되고, V-가 -5V에 연결된다면 어떤 일이 벌어지는지 실험을 통해서 살펴보자. 100mVp, 1KHz 정현파 (DC offset은 0V)와 200mVp, 1KHz 정현파를 각각 인가하여 실험을 해보자.

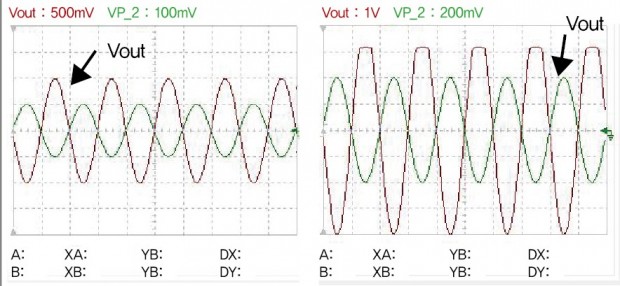

그림 2-2. V+에는 3.3V, V-에는 -5V를 인가한 Op Amp.의 출력 파형 그림 2-2는 TINA의 오실로스코프 화면을 캡쳐하여 옮긴 것으로 DC를 차단하지 않고 있는 그대로 Y축 스케일만 조정하여 화면에 잘 나오도록 하였다. 각각의 그림에서 큰 진폭의 정현파가 출력 파형이다. 전원이 비대칭으로 공급되었음에도 불구하고, 그림 2-2의 좌측 그래프를 보면 출력신호가 0V를 기준으로 아래 위로 아름답게 진동하고 있다. 우측 그래프를 보면 역시 0V를 기준으로 진동을 하는데, 상반구 쪽에서 잘리는 현상이 관찰된다. 비대칭 전원을 공급해도 기준점 0V에는 변화가 없고, 출력 신호의 진동폭에서만 차이가 난다. 이 이유는 Op Amp.를 구성하는 회로를 살펴보면 쉽게 이해할 수 있기에 다음절로 좀 미루자. 다음 절에서 트랜지스터 레벨의 설명을 간단 명료히 다루고 있으니, 위 실험 결과를 토대로 증폭기의 AC 특성을 해석하는 데 있어서 DC 전원단은 전혀 고려하지 않아도 되는구나 하고 넘어가자. Ideal Op Amp.에 DC 전원 공급 회로가 없는 이유이기도 하다. 하지만, 그림 2-2의 우측 그림을 보면, 상반구에서 정현파가 잘린 것을 확인할 수 있다. V+가 3.3V이기에 3.3V 이상을 표현하지 못하기 때문이다. 그렇다면, 0.5Vp, 1KHz 정현파를 입력한 후 출력에 어떤 변화가 있는지 살펴보자. 그림 2-1의 회로는 반전 증폭기로 증폭비는 10배이다. 따라서, 출력으로는 5Vp, 1KHz 정현파가 나와야 한다. 회로에 대한 자세한 설명은 다음절에서 시작한다.

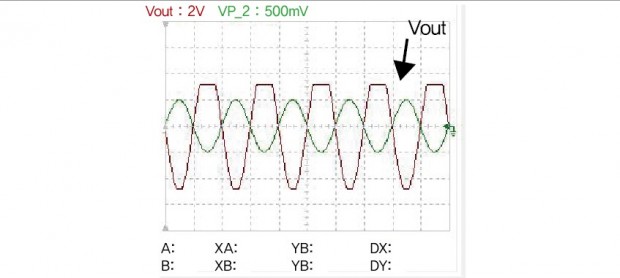

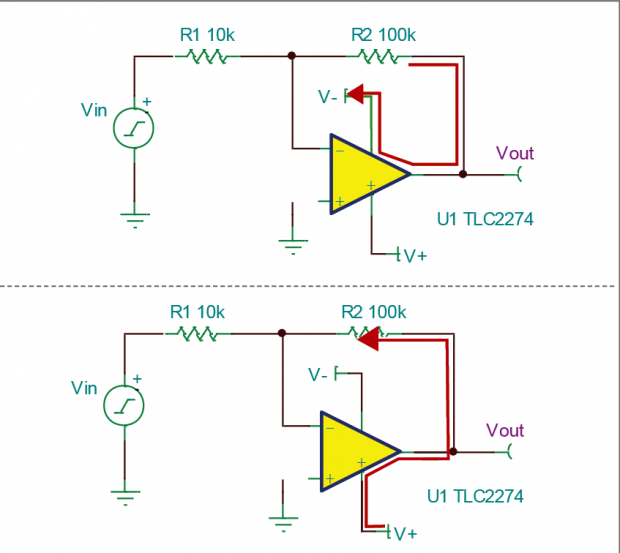

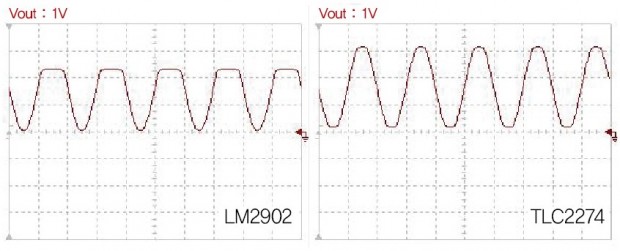

그림 2-3. 0.5Vp, 1KHz 정현파를 입력한 경우, 입력과 출력파형 그림 2-3을 보라. 상반구 뿐만이 아니라 하반구도 좀 잘렸다. 잘린 부위의 전압을 읽어보면, 각각 3.19V와 -4.83V 정도로 측정된다. 공급전압은 각각 +3.3V와 -5V인데, 출력전압은 이에 못 미친다. Op Amp. 세계의 어휘로는 출력 Swing 폭이 공급 전압에 못 미친다. 라고 표현하는데, 이 정도면 사실 굉장히 우수한 편이다. TLC2274가 Rail-to-Rail Input Output(RRIO) 구조이기에 가능한 결과다. RRIO가 뭔지는 3절에서 확인하도록 하고 먼저 그 특성을 확인해보자. RRIO 방식을 채택하지 않은 Op Amp.와 출력을 서로 비교해보면 차이를 확인해볼 수 있을 것이다. 널리 쓰이는 LM2902를 비교대상으로 선정했다. 각각 그림 2-1 회로처럼 꾸며놓고, +/-5V 전원을 공급했다. 이어서, 0.5Vp, 1KHz 정현파를 인가한 후 출력파형을 측정하였다. 그림 2-4를 살펴봐주시기 바란다. 좌측이 LM2902의 출력이고, 우측이 TLC2274의 출력이다.

그림 2-4. LM2902와 TLC2274의 출력 진동폭 비교 그림 2-4를 보니, LM2902의 경우 상반구에서 좀 더 심하게 잘렸다는 것을 확인할 수 있다. 각각의 상한치와 하한치를 측정해보니, LM2902는 4.01V와 -4.92V로 측정된다. TLC2274는 +/-4.82V로 측정된다. LM2902의 스윙(Swing)폭은 혹은 진동폭은 8.93V이고 비대칭이며, TLC2274의 스윙폭은 9.64V이며 대칭이다. 일단 스윙폭은 TLC2274가 더 넓다. 만약 하반구쪽 신호만 있어도 충분하다면, LM2902가 더 우수하다고 할 수 있다. Envelope Detector(포락선 검출기)처럼, 하반구나 상반구, 반쪽만 있어도 되는 그런 분야도 있지만, 일반적으로 상/하반구 모두 온전한 출력을 필요로 하는 경우가 대부분이다. 이때, RRIO방식을 채택한TLC2274는 잘림 정도가 대칭이고, 스윙폭이 더 크기에 보다 적절하다고 하겠다. 세부적으로는 RRI(Rail-to-Rail Input) 방식이 있고, RRO(Rail-to-Rail Output) 방식도 있으며, RRIO도 있다. RRIO를 쉽게 설명하기 위해서는 회로 레벨까지 내려가야 하는데, 이렇게 되면 트랜지스터 원리까지 설명해야 해서 걱정이 제법 된다. 트랜지스터가 싫어서 Op Amp.를 사용하시는 분들도 계실텐데, 트랜지스터 없이 RRIO를 설명하자니, 내공이 딸려서, 부득이 트랜지스터를 조금 빌려서 설명을 했다. 트랜지스터에 대한 언급을 최대한 자제한 채, 회로만 가져다 놓고 설명을 했으니, 조금만 참고 다음 절을 읽어봐 주시기 바란다. 개념만 이해하면 된다. Op Amp.를 선택하는데 있어서 꽤나 유용하게 쓰이니 꼭 다음 절을 읽어봐 주시기 바라며, 이제는 Op Amp. 내부에서 이뤄지는 전류 흐름에 관해 얘기해보자.

그림 2-1 회로로 돌아가서 전류가 어떻게 흐르는지 고찰해보자. Op Amp. 의 궤환(Feedback)을 담당하는 R2 100K 옴 저항에서의 전류 흐름을 한번 생각해보자. 출력단에 부하는 안 걸려있다. 지금 이 순간 R2에서의 전류 방향은 오른쪽이다 라고 가정하자. 그렇다면, 이 전류의 최종 종착점은 어디인가? 다음 순간에 R2에서의 전류 방향이 왼쪽으로 바뀌었다면, 어디로부터 전류가 나와서 R2에다가 왼쪽 방향 전류를 만들어 내는가? 만들어 낼 곳이 Op Amp. 밖에 더 있는가? Op Amp.는 DC 전원단으로부터 에너지를 공급받아 출력 신호를 생성해낸다. 이 부분이 커패시터나 인덕터와 다른 부분이다. 그래서, 능동(Active) 소자라고 한다. 발산의 위험도 있다. 그림 2-5를 보자.

그림 2-5. Op Amp.에서 전류의 흐름 그림 2-5회로를 보면, Op Amp. 가 전력을 소비하는 과정을 떠올릴 수 있을 것이다. V+ 전원 핀에서는 전류를 공급하고, V- 전원 핀에서는 빨아들인다. 이 과정에서 전력이 소비되는 것이다. 전원 핀이 생략된 이상적인 Op Amp. 만을 놓고, 그림 2-5와 같은 전류의 흐름을 생각하기는 솔직히 쉽지 않다. 초보 엔지니어에게 R2에 흐르는 전류는 어디로 가는가 하고 물어보면 대부분 머뭇머뭇 한다. 이러한 내용을 충분히 이해하고 있다는 가정하에 이상적인 Op Amp.를 만들어 놓은 것인데, 가정이 제대로 성립되지 못한 엔지니어들한테 Op Amp.에 관한 내용을 주입했다가는 사상누각 사태가 벌어질 수도 있는 것이다. 이번 기회에 기본을 확실히 해두도록 하자.

3. Rail to Rail Input Output(RRIO) 방식의 장점

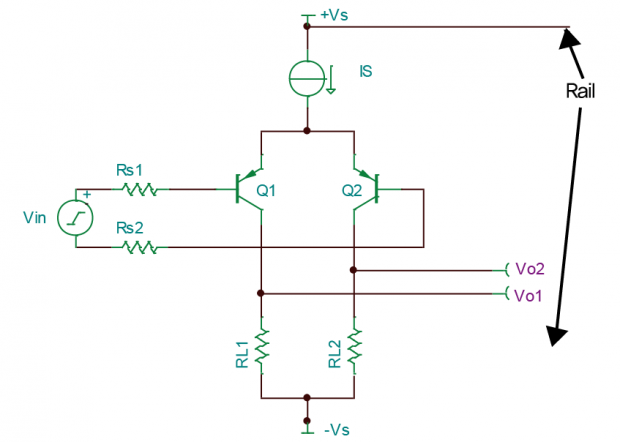

최근 들어, 저 전압용으로 개발되는 Op Amp.는 거의 다 RRIO 방식을 채택하고 있는데, 이 RRIO 방식을 단순히 출력 진동폭을 최대화 할 수 있는 구조 정도로 받아들이고 넘어가기에는 좀 찝찝해서 이 절을 준비했다. 왜 그런지 이해하기 위해서는 트랜지스터 수준에서의 회로 설명이 필요한데, 트랜지스터에 관한 설명은 최대한 억제한 채, 최대한 이해하기 쉽도록 각고의 노력을 기울여서 설명하였으니, 찬찬히 읽어봐 주시기 바란다. 일단, LM2902처럼 RRIO 방식이 아닌 일반적인 Op Amp.의 입력단 회로를 간략히 그려서 그림 3-1에 올려두었다. 모든 Op Amp. 에는 Voltage Rail 이 있다. 보이는가? 그림 상단에 +DC 전원 공급단 +Vs가 보이고, 하단부에는 -DC 전원 공급단 -Vs가 보인다. 이게 Op Amp. 전체 회로에 공급되는 전원이기에 전체 회로도를 그리면 마치 기차 레일처럼 길게 늘어진다. 그래서 Rail이다. 그렇다면, Rail-to-Rail은 무슨 말인가? LM2902에도 Voltage Rail이 있는데, RRIO 방식이 아니라고? 궁금해요? 궁금하시면, 계속 읽어 나가보자.

상단부 전원단 바로 아래에 전류원 Is가 보이고, 하단부에는 전류원이 없고 부하저항 RL1과 RL2만 보인다. 예를 들어, RL1이나 RL2에 전류가 거의 흐르지 않는다면, RL1과 RL2에서 전압 강하가 거의 없기에, Vo1이나 Vo2는 -Vs가 된다. 즉, Vo1이나 Vo2가 down to the bottom voltage rail 이 된다. 반대로 전류가 많이 흐르는 경우를 고려해보자. 전류가 많이 흐르면, RL1이나 RL2에 전압강하가 많이 발생한다. 흐르는 전류를 각각 I1과 I2라고 한다면, Vo1은 -Vs + I1RL1 이 된다. 이 값이 아무리 커진다고 한들 +Vs에 미치질 못한다. 왜냐면 Q1과 Q2에서 전압 강하가 발생하고, 전류원 Is에서도 전압강하가 발생하기 때문이다. 이런 구조로 인해서 그림 2-4의 좌측에서 보듯이 Op Amp. 출력 신호 상반구에서 심한 왜곡을 보이는 것이다. 비 RRIO 구조의 출력 특성이다.

그림 3-1. LM2902의 입력단 구조 다음은 RRI(Rail-to-Rail Input) 구조이다. 구조가 조금 복잡하지만 전부 다 이해할 필요는 없다. RRI 방식을 이해하는데 도움이 될만한 부분이 있어서 그려본 것 뿐이다.

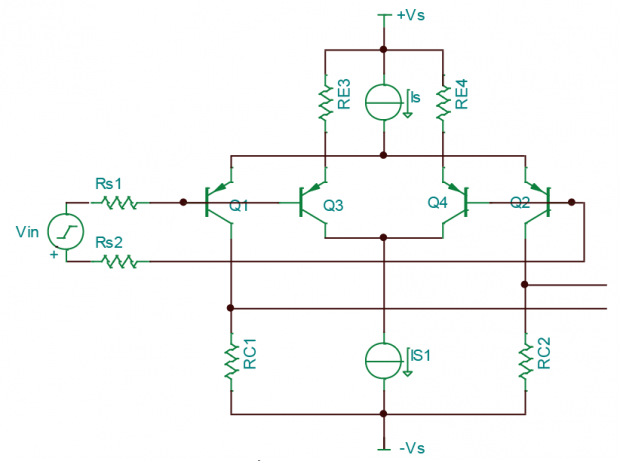

그림 3-2에서 Q1 ~ Q4는 트랜지스터다. 트랜지스터 그림에서 화살표가 그려진 단자를 에미터(Emitter)라고 한다. Q3와 Q4 에미터에는 RE3와 RE4저항이 달려있다. 그런데, 전류원 Is의 상부측이 RE3 및RE4의 상부측과 똑같이 +Vs에 묶여 있기에 트랜지스터의 에미터 전압이 +Vs까지 상승할 수 있다. 오호라, 전류원에 의한 전압 상승 제한폭이 사라진 구조구나 하는 것을 알 수 있다.

그림 3-2. RRI 구조 RC1과 RC2가 달려있는 트랜지스터의 단자는 컬렉터(Collector)라 한다. 나머지 단자를 베이스(Base)라고 하는데, 베이스에 입력된 전류가 증폭이 되어서, 에미터와 컬렉터 사이에 흐른다. 이 구조가 좌우로도 대칭이지만 아래 위로도 대칭이다. 왠지, TLC2274의 출력 신호가 대칭인 이유가 여기에 있는 것도 같다. (사실은 출력 회로까지 상하로 대칭이어야 하는데, 어쨌든 냄새가 좀 난다.) 그림 3-2회로 역시 출력 신호는 컬렉터에서 취하고 있다. 출력 신호가 위쪽으로 커질때면, 오로지 트랜지스터에서 발생하는 전압 강하(에미터와 컬렉터 사이의 전압)에 의해서만 제한을 받는다. Is에 의한 영향은 사라졌기에, 진동(Swing)폭이 좀 더 늘었다. 이는 RRI(Rail-to-Rail Input) 방식의 장점으로 비 RRI 방식에 비해 입력 신호를 좀 더 크게 받아들일 수 있다. 다시 말해, Op Amp.의 입력 신호를 작게 만들 필요가 줄어든다는 얘기다.

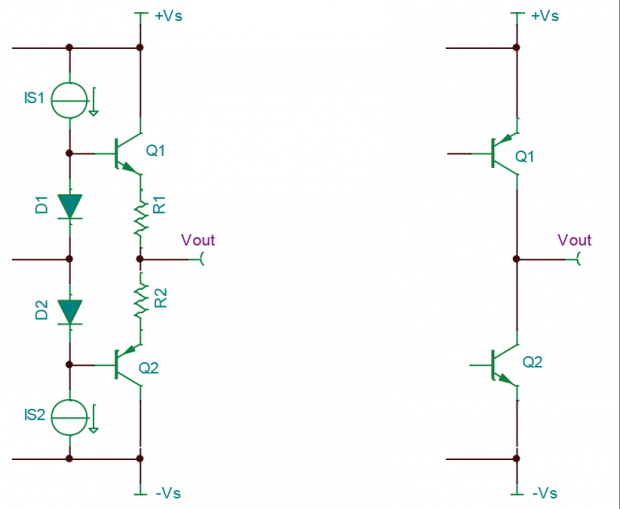

출력의 경우는 입력과 상황이 조금 다르다. 트랜지스터에 의한 전압 강하 때문에 진정한 RRO 방식을 만들기 어렵기에, RRO 방식이든 아니든 최대한 진동폭을 키우기 위해 나름대로 많은 애를 쓰고 있다. 이중에서 널리 쓰이는 두 가지 방식을 비교해보도록 하겠다.

그림 3-3. Op Amp. 출력단 비교 그림 3-3의 좌측 회로는 아주 널리 쓰이는 Class AB 급 증폭기, 즉, Push-Pull 방식 증폭기로 Op Amp. 출력단에 널리 쓰이는 대표적인 회로이다. HiFi 오디오에도 많이 채용되는 방식이며, LM2902도 채택한 방식이다. 이 방식의 장점은 출력 임피던스를 매우 작게 만들 수 있다는 점이다. 단점은 출력 신호의 진동 폭이 트랜지스터(Q1, Q2) 와 저항(R1, R2)에 의해 제한되어 그다지 넓지 못하다라는 점이다. 이걸 극복한 것이 우측 회로인데, 트랜지스터의 극성이 좌측과 다르다 라는 점에 주의해야 한다. 이 방식은 출력 스윙폭을 극대화할 수 있지만 출력 임피던스(BJT의 경우 )가 그다지 적지 않다는 단점이 있다. 또 다른 단점으로는, 출력 전류가 점점 높아지면 트랜지스터의 컬렉터와 에미터 사이 전압도 점점 커져서 출력 신호 진동의 궁극 목표인 Rail-to-Rail, 즉, V+에서 V-까지의 스윙에서 멀어진다. TLC2274는 FET로 구현된 Op Amp.이기에 출력단 역시 FET로 구현되어 있다. 그림 3-3 우측 회로에서 상단 트랜지스터가 PMOS(Positive Metal Oxide) 트랜지스터이고 하단 트랜지스터가 NMOS(Negative) 트랜지스터로 구현되어 있다. 이 경우가 좀 더 RR스럽다. 왜냐면, MOS 트랜지스터의 채널 저항을 BJT의 출력 저항보다 훨씬 작게 만들 수 있기 때문이다. 하지만, 이것 역시 출력 전류가 커지면 채널간 전압 강하도 커지기에 Rail-to-Rail의 목표에서 벗어난다. 현재까지는 RRIO 방식이 최대의 출력 신호 진동폭을 보장하기에, 특히, 저전압 시스템에서는 RRIO 방식을 채택한 Op Amp.가 사실상 필수 선택이다. 그렇지 않을 경우, 신호의 진동폭이 제한되어 버려서 비싼 돈주고 고른 ADC등에서 분해능 손실을 톡톡히 치르게 된다. RRIO, 꼭 명심하자.

마지막으로 다음 그림을 보고, RRIO 방식 이해를 마무리 짓도록 하자. 그림 2-1의 회로와 동일한 회로를 꾸며놓고, V+에는 3.3V를 걸고, V-에는 0V를 걸었다. – 입력단에는 0.165Vp, 1KHz 정현파를 인가하였다. + 입력단에는 적절한 DC 오프셋(Offset) 전압을 인가하여, 출력 신호가 1.65V를 기준으로 진동하도록 만들었다. DC 오프셋을 인가하는 방법은 4.8절에서 자세히 다루니 지금은 단순히 잘 인가했구나 라고 생각하자. 그림 2-1 회로의 증폭비는 10배이다. 이상적인 Op Amp.라면, 1.65V를 중심으로 1.65Vp의 정현파가 출력 되어야 한다. 다음 그림을 잘 보자. 좌측이 LM2902 출력이고, 우측이 TLC2274의 출력이다.

그림 3-4. LM2902와 TLC2274의 출력 비교 먼저, 그림 3-4의 좌측 파형은 LM2902에서 채취한 것인데, 최대 및 최소치가 각각2.31V와 0.07V 이다. 중심이 1.65V이다보니, 상향으로는1V를 상승하지 못하는 부실한 출력을 보여주지만, 하향으로는 0.07V까지 내려올 수 있기에 좋은 결과를 보여준다. 하반구 신호만 사용해도 충분한 시스템이라면 LM2902가 상당히 좋은 성능을 유도할 수 있겠다. 그림 3-4의 우측은 TLC2274의 출력으로, 비록 아래위가 좀 뭉그러졌지만, 1.65V 기준으로 아래위 대칭적으로 잘 진동하는 것을 볼 수 있으며, 좌측과 확연히 비교가 된다. 최대 및 최소치는 각각 3.13V와 0.17V다. 1.65V를 중심으로 거의 +/-1.5V를 진동할 수 있기에, 3.3V 단일 전원 시스템에서는 거의 최고 수준의 진동폭을 보여준다고 할 수 있겠다. LM2902의 진동폭은 2.24V(=2.31-0.07)이고, TLC2274의 진동폭은 2.96V이다. 만약, 0~3.3V의 입력범위를 가지는 16비트 ADC를 LM2902로 구동한다면, 입력 범위의 67.9%밖에 사용하질 못한다. 비싼 돈 주고 산 ADC가 제 역할을 하지 못하는 경우다. TLC2274의 경우는 약 89.7%를 사용한다. 그나마 값도 좀 저렴하고 해서 3.3V 저전압 단일 전원용으로 TLC2274가 많이 쓰이고 있는 것이다. 그림 3-4는 RRIO 방식과 비 RRIO 방식을 비교해주는 적절한 사례라고 하겠다.

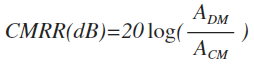

4. CMRR과 PSRR

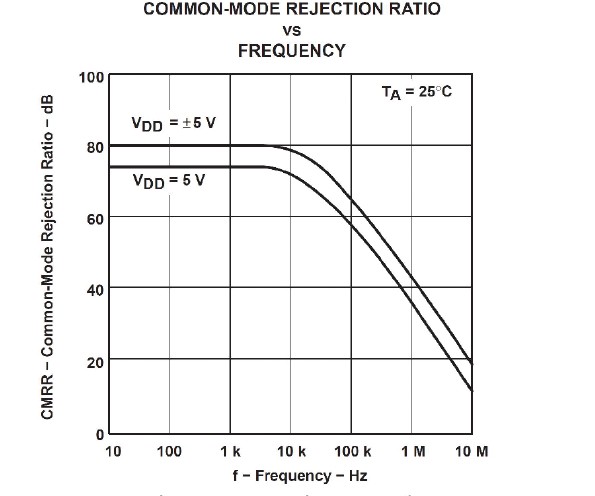

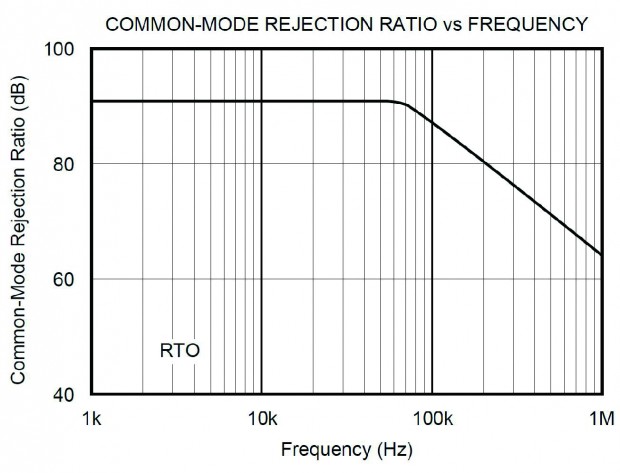

먼저 CMRR부터 얘기해보자. CMRR은 Common Mode Rejection Ratio의 앞머리글자다. 한문으로 옮기자면 동상신호제거비율 정도라고 할 수 있겠다. Op Amp.는 기본적으로 차동 증폭기이다. 차동이라함은 Op Amp.의 두 입력단에 인가되는 신호의 차이를 말한다. 이 차이를 증폭함과 동시에 그 차이가 없는 동상 신호, 즉, 두 입력단에 공통된-Common Mode- 신호는 감쇠시킨다. 그 감쇠비율이 CMRR이다. CMRR이 높을수록 좋은 차동증폭기가 된다. 예를 들어, CMRR이 매우 높다면, 두 입력단에 동일하게 유입되는 외부 노이즈는 별도의 필터없이 높은 비율로 걸러 내어진다. 멋지지 아니한가? 혹은 두 입력단에 동일하게 유입된 DC 전압 이라던지, 혹은 60Hz 전원에 의해 발생한 노이즈 등은 별도의 필터링 과정없이 Op Amp. 특유의 성질인 CMR(Common Mode Rejection) 기능에 의해 제거 된다는 것인데 대단하지 아니한가? 그림 4-1은 TLC2274제품 설명서에서 CMRR그래프를 옮긴 것이다.

그림 4-1. TLC2274의 CMRR 그래프 제품 설명서에서는 CMRR이 통상 75dB라고 밝히고 있다. 그래프를 보면, +/-5V, 즉, 양전원을 이용했을 때의 CMRR그래프가, +5V 단일전원을 사용했을 경우보다 약 5dB 가량 높다는 것을 확인할 수 있다. LM2902의 CMRR은 80dB로 나와있다. LM2902가 5dB 가량 우수하다고 할 수 있을텐데, 과연 그럴까? 5dB라 함은 LM2902가 동상 신호를 TLC2274에 비해서 약 1.78배 더 억제 시킨다 라는 것이기에 이는 상당한 수치다. 하지만, 여기에 혹하면 안된다. 그래서 이 책과, 이 절이 준비된 것이다. CMRR은 주파수에 대한 함수로 나타난다는 점을 명심해야 한다. 그림 4-1을 보라. CMRR의 코너 주파수는 대략 10KHz로 보이고, 감쇠비율은 대략 -20dB/decade 로 보이는데 실제로 그러하다. LM2902의 CMRR 그래프는 제품 설명서에 없어서 못 옮겼는데, 대개 비슷한 패턴을 보인다. 다만, 코너 주파수가 다르기에 코너 주파수가 높을수록 좋은 CMRR 특성을 보이는구나 라고 판단 해야 한다.

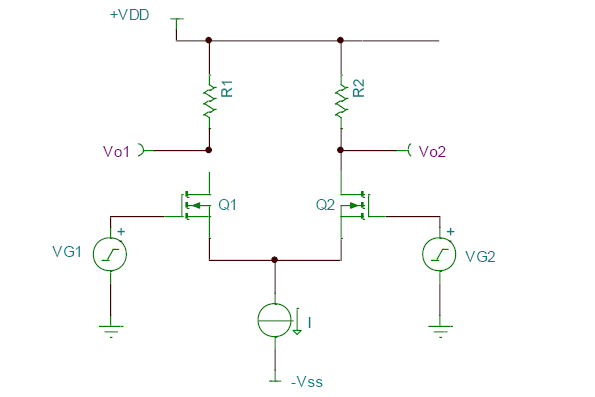

CMR 기능을 정확하고 손쉽게 이해하기 위해서는 트랜지스터 레벨에서 차동 증폭기를 살펴봐야 하는데, 트랜지스터에 대한 기초적인 부분까지 설명하려니 양이 너무 많아지는 것 같고, 책 주제를 벗어나는 것도 같아 갈등을 많이 했다. 그렇다고, 트랜지스터의 도움없이 설명을 하자니 능력이 모자라서 진도가 나가지 않기에 부득이 트랜지스터의 힘을 조금 빌렸다. 이 점 깊은 양해를 구한다. 트랜지스터에 대해서는 최대한 간단하고 단순하게 다루고, CMR에 초점을 맞추어서 설명하고자 하니 페이지 넘기지 마시고 계속해서 읽어 나가봐 주시길 바란다. 동상 신호가 제거되는 원리만 살펴 본 후, 다시 Op Amp.로 즉시 넘어오니 채널고정이 아닌 책 고정 해주시면 감사하겠다.

Op Amp. 는 대게 30 ~ 40개의 트랜지스터로 구현된다. Op Amp의 첫번째단은 입력단으로 차동 증폭기(Differential Amplifier)로 구현되어 있다. 그러기에 입력 핀이 +/- 2개이다. 그 다음 증폭단도 차동 증폭기로 구현되어 있는 것이 대부분이며, 마지막 단은 단동(Single Ended) 증폭기로 구성되는 것이 일반적이다. 마지막 출력단까지 차동 증폭기로 이뤄져 있으면서 차동으로 출력되는 증폭기를 Fully Differential Amplifier라고 하는데, 이는 9절에서 자세히 다룬다. 각 단에 설계된 차동 증폭기가 CMR 기능을 제공하고 있는데, 트랜지스터로 구성된 차동 증폭기를 그림 4-2에서 보도록 하자.

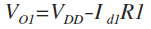

그림4-2. FET로 구현된 차동 증폭기 그림4-2의 회로는 현재 동작이 잘 된다라고 가정을 하자. 이를 Bias가 제대로 잡혔다 라고 말한다. Q1과 Q2는 Field Effect Transistor, 줄여서 FET라고 한다. Q1과 Q2 의 심볼을 보면 화살표가 점선을 가르키고 있는 것을 볼 수 있다. 점선은 몸통을 표시하는데, 이게 점선인 이유는 특정 조건이 되면 이 점선이 이어져서 전류가 흐르는 채널이 형성되기에 그렇다. 화살표는 반도체 극성을 말한다. 정식으로 쓰자면, Enhanced Metal Oxide P-type Semiconductor Field Effect Transistor 인데, 이 정도까지 알고 계신다면 이미 훌륭한 상태이신 것이고 모른신다고 한들 전혀 상관없다. Vo1과 Vo2가 인출된 트랜지스터의 다리를 드레인(Drain)이라고 하는데 이것도 몰라도 된다. VG1과 VG2가 인가된 핀을 게이트(Gate)라고 하고, I 라는 전류원이 연결된 핀을 소스(Source)라고 하는데 전혀 몰라도 된다. 그저, FET라는 트랜지스터는 Gate 에 인가되는 전압에 의해서 드레인-소스간에 흐르는 전류량이 제어되는 구나 라고만 알아두면 더 이상도 필요없을 만큼 적당한 수준이지만, 이것마저도 몰라도 된다. 머리속에서 회로를 한번 구동 시켜보자. VG1이 변하면, Q1의 드레인-소스간 전류가 변한다. 즉, R1에 흐르는 전류가 변한다. R1을 통해서 Id1 이라는 전류가 흐른다고 하자. 그렇다면 Vo1 전압은 다음과 같다.

수식에서 보듯이, Q1이 어떻고 드레인이 어떻고, 게이트가 어떻다는 말이 전혀없다. 참고로, MOSFET에서 Id1은 VG1과 2차 함수 관계가 있고, 기하학적 구조, 즉, 트랜지스터 면적에 비례하고 채널 길이에 반비례 관계가 있다. 이것까지 알면, FET 가 순한 양으로 바뀔 것인데, 우리는 Op Amp를 사용하기에 이런 내용이 전혀 필요 없다. 동일한 방식으로 Vo2를 구하면,

이다. 일단, VDD를 공통으로 사용하고 있는데, 반도체 정밀 공정 덕에 Q1과 Q2의 면적 등이 모두 동일하고, 도핑 농도까지 모두 동일하며, R1과 R2가 동일하다면 (실제 CMOS 공정에서는 R1, R2대신에 트랜지스터로 부하를 만들어서 더 높은 이득을 얻고 있다.), 정확히 V01==V02이다. 의심의 여지는 전혀 없다. 그렇다면, V02-V01는 얼마인가? Q1과 Q2의 양단에서 출력의 차이를 취하다 보니, Id1==Id2라면, 즉, 트랜지스터의 동일한 입력 신호는 상쇄되어버리는 결과를 얻게 된다. 즉, 동상 제거 능력이 생기는 것이다. 그런데, 어떻게 Q1과 Q2가 똑같겠는가? 뭐가 달라도 조금씩 다르지 않겠는가? 게다가 반도체 속성상 어쩔 수 없이 발생하는 기생 커패시턴스 성분과 증폭기의 주파수 보상 문제 때문에 어쩔 수 없이 장착해야 하는 커패시터 때문에 CMRR이 주파수 함수로 나타난다. 어쨌든, 차동 증폭기를 입력단으로 사용하는 모든 Op Amp.는 동상신호제거능력을 가지고 있다. 이제 Op Amp.로 넘어와서 동상신호 제거능력을 관찰해보도록 하자.

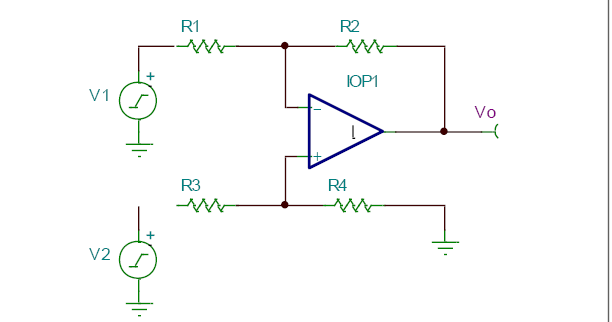

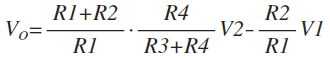

그림 4-3의 Op Amp. 회로를 보도록 하자. Op Amp.로 구현한 Difference Amplifier 회로이다. 번역하자면 차분증폭기다. 차동 증폭기가 아니라, 차분 증폭기. 말장난같지만, 둘은 엄연히 다르다라고 주장하시는 분들이 많지만, 그다지… 입출력관계를 구해보면 두 입력단의 차가 증폭되기에 Difference라는 말이 붙었는데, 차동 증폭기와 동작원리는 동일하니 이름에 현혹되지 마시길 바란다. 굳이 이름을 달리한 기준을 말하자면, 입력 값이 중앙값을 기준으로 동일한 수준의 차이를 보이는 경우를 차동 증폭기라고 한다. 단순히, 그냥 차이를 증폭하면 차분증폭기라고 하는데, 뭐 어떠랴 같다고 보자. 회로도 사실상 같다.

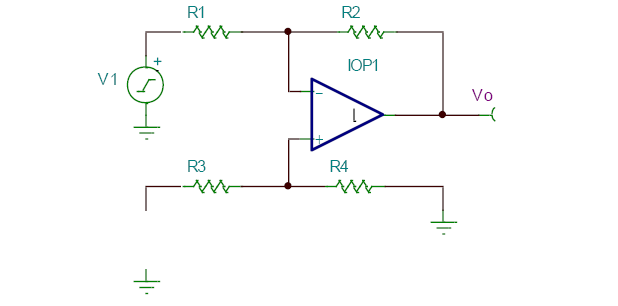

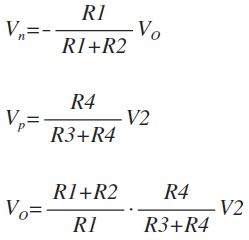

그림 4-3. 차분 증폭기 Vo를 구해보실 수 있겠는가? Op Amp. 회로에서 입력신호원이 2개 이상일 때에는 중첩의 원리를 적용하면 정말로 쉽게 풀린다라는 점 떠올리셨는가? 한번 풀어보자. V1에 의한 출력을 구하려고 한다면, V2의 영향을 없애야 한다. 전압원이니 단락(Short)시키면 된다. 따라서, 다음의 회로로 바뀐다.

그림 4-4. V2 영향을 배제한 회로 그렇다면, Vo는? 쉽게 구할 수 있다. 왜냐면, Op Amp.의 입력 전류는 0 이기에 R3와 R4의 영향은 없다. 그냥 접지와 바로 연결된 것과 같다. 흔히 보는 반전 증폭기 회로가 된다. 따라서, Vo는,

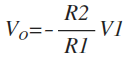

이다. 이제 V2에 대한 Vo를 구해보자. 회로는 다음과 같이 변한다.

그림 4-5. V1 영향을 배제한 회로 흔히 보는 비반전 증폭기다. 사실 비반전 증폭기라는 말도 웃긴다. 그냥 증폭기라고 하면 될 것을 말이다. 비반전 증폭기라는 말을 쓰면, 그냥 ‘증폭기’는 뭔가? 그냥 증폭기와는 다른 증폭기인가? 하고 오해를 부를 수 있기 때문이다. 혹시나 헷갈릴까봐 이런 용어를 쓰신 것 같다. 증폭기는 반전 증폭기와 비반전 증폭기로 이뤄져 있다고. 이제부터 그냥 증폭기라고 하면 입력과 출력이 동위상인 일반적인 증폭기, 즉, 비반전증폭기를 의미하는 것으로 이 책에서는 규정하겠다. 전달함수를 구해보자. 3장에서 열심히 구했었는데, 기억이 나실런지 모르겠다. 이러한 형태의 증폭기 전달함수를 구하는 쉬운 방법은 Op Amp.의 또 다른 중요한 성질 중에 하나인 두 입력단의 전압은 같다 라는 성질을 떠올리시면 좋겠다. 즉, 두 입력단의 전위차는 늘 0 이다 라는 점을 이용하는 것이다. 즉, 그림에서 Vn 과 Vp 는 같다라고 관계를 설정하고 풀면 된다.

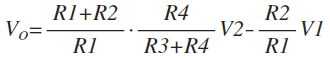

중첩의 원리를 이용해서 수식 (4-1)과 합치면,

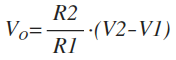

이 된다. 이 수식이 V0=A(V2-V1)형태의 차분(혹은, 차동) 증폭기가 될려면, R4=R2, R3=R1로 설정하면 된다. 이렇게 설정하면, 수식 4-1은 다음과 같이 이쁘게 변신한다.

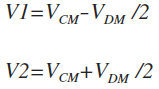

즉, V2와 V1의 차이를 증폭하는 회로가 되는 것이다. 그런데, V2와 V1는 다음과 같이 동상전압과 이상전압의 합성된 형태로 표현할 수 있다.

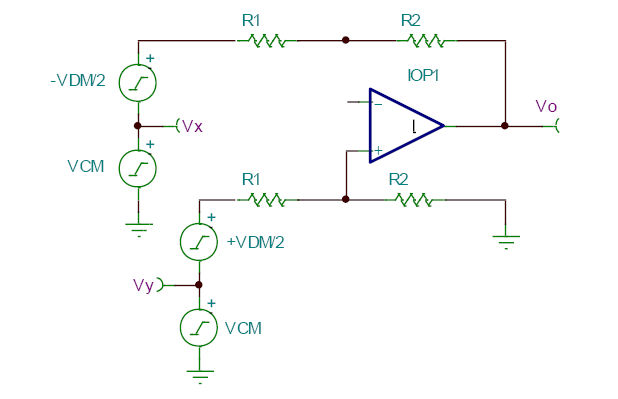

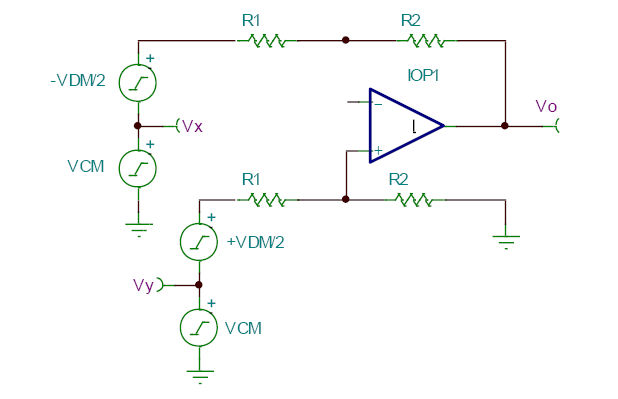

위 수식에서 VCM은 공통 성분, VDM은 서로 다른 성분을 말한다. 이 수식을 토대로 그림 4-3 회로를 그림 4-6처럼 바꿔 볼 수 있겠는가?

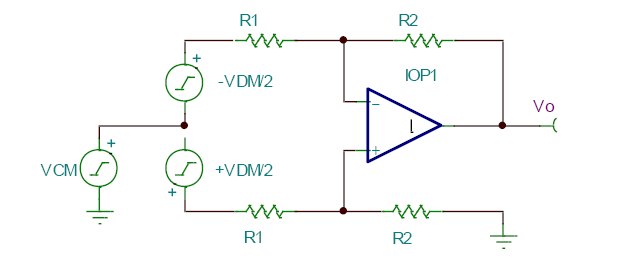

그림 4-6. 입력을 동상 신호와 이상 신호로 구분한 회로 V1에 쪽에 달린 신호원에 음의 기호를 할당한 것은, V1 과 VDM/2의 관계가 반전이기 때문에 그런 것이다. 그림 4-6에서 Vx와 Vy의 전압이 VCM만큼은 서로 동일하기에 한데 묶을 수가 있다. 그렇다면, 그림 4-7과 같이 된다. 등가 회로의 원리를 잘 떠올리시면 된다.

그림 4-7. 그림 4-6 등가 회로 : VCM을 공통으로 처리 그림 4-7처럼 신호원을 쪼개서 그린 이유는, 동상 신호와 이상 신호의 관계를 쉽게 파악할 수 있기 때문이다. 먼저, ±VDM/2=0이라고 해보자. VCM이 바뀐들 VO에 무슨 영향이 있을까? 즉, 동상 신호는 Op Amp.의 기본 속성에 의해서 아주 손쉽게 걸러 내어진다. 이것이 CMR(Common Mode Rejection)이다. CMR 기능이 이해되시는가? 그런데 주의할 점이 하나 있다. 실전에서는, Op Amp. 뿐만이 아니라 저항에도 오차가 존재한다는 점이다. Op Amp.도 이상적이지 못해서 속상한데 저항까지 말썽이다. 사실은 저항이 더 큰 영향을 미치기에 다음 내용이 준비된 것이니 계속 읽어나가 주시길 바란다. 실제로는, Op Amp. 자체의 CMRR과 외부 결선까지 포함한 CMRR 중에 낮은 CMRR이 전체 CMRR을 결정한다. 따라서, 이미 Op Amp.를 선정했다면, 외부 결선으로 인한, 즉, 저항 등의 오차로 인한 CMRR 저하는 결단코 피해야 한다. 그림 4-8 회로는 저항 오차를 감안하여 꾸민 회로이다. 오차가 존재하는 저항으로 차분 증폭기를 구현했을 경우인데, 계산 편의상 오차가 한 저항에서만 발생했다고 가정하자. 그 영향을 이해한 후에 모든 저항에 오차가 발생하면 어떻게 될까 하는 것을 고찰하는 것으로 충분하다.

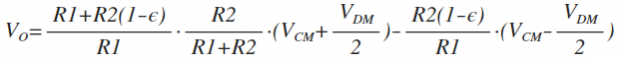

그림 4-8. 저항 오차로 인한 CMR 영향 그림 4-8은 Op Amp.의 궤환(Feedback) 경로에 위치한 R2 저항에 오차가 -εR2만큼 발생했다고 가정한 것이다. (TINA에서는 ε가 표시가 안되어서 e로 표시했음을 양해바란다.) 입출력 관계식을 구해보자. 수식 4-2를 이용하면 편리하겠다. 수식 4-2는 다음과 같다.

이 수식에서, R4=R2, R3=R1이고, R2가 R2(1-ε)임을 주의하시기 바란다. 그리고, V1=VCM-VDM/2이고 V2=VCM+VDM/2이다. 위 수식에 각각 대입하면,

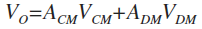

가 된다. CMRR(Common Mode Rejection Ratio)를 구하기 위해서, 그림 4-8의 전달함수를 다음과 같은 식으로도 구해보자.

중첩의 원리를 약간 다르게 적용한 수식이다. 즉, 입력 신호중에 동상신호는 동상신호 증폭비율만큼 증폭되고, 이상신호는 이상신호 증폭비율만큼 증폭될 것이니, 각각을 구하여 중첩하면 원하는 결과가 나온다 라는 것을 반영한 수식이다. 수식 4-3을 수식 4-4처럼 재구성해보자. 이렇게 하면, CMRR 구하기가 쉽다. 왜냐면, CMRR의 정의가 다음과 같기 때문이다.

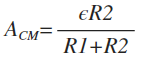

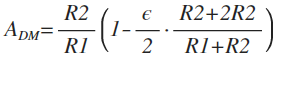

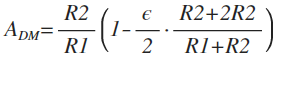

(4-4-2) 수식을 정리하여, ACM과 ADM을 구하면,

이다. 전혀 어렵지 않게 유도할 수 있다. 수식이 너저분하다고, 전개과정마저 너저분하겠지 하는 것은 오판이다. 매우 깔끔한 편이니 꼭 해보시길 바란다. 수식에 대한 트라우마로 인하여 책을 덮어버리는 불상사는 없기 바란다. 전개과정이 무척 쉽다. 위 수식에서 ACM과 ADM은 각각 다음과 같다.

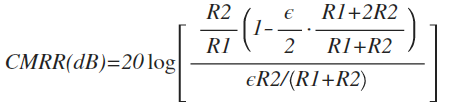

CMRR의 정의에 대입하여 CMRR을 구해보면,

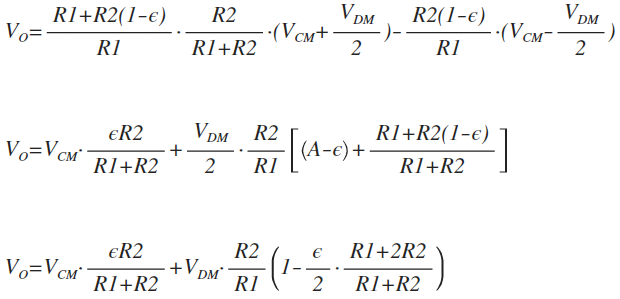

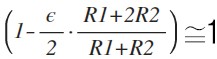

이다. 이 수식은 그다지 아름다워 보이지 않는다. 죄송하다. 수식도 복잡하고 마음도 복잡하다. 계산기에 입력해두고 사용하면 된다고 할지라도, 입력하는데 상당한 시간이 걸리고, 오입력의 경우도 즐비하겠다. 그래서 위 수식을 아름답게 만들어 보자. 적당한 오차를 허용하여 간략화시키는 것이다. 엔지니어링은 이런 것이 맛이 아닌가? 먼저 ADM을 살펴보자.

ε가 1% 이하 수준이라면 이라고 할 수 있다. 아름답다. 오일러 할아버지가 아름답다고 한 숫자 중에 으뜸이 1이다. 이걸 적용하여 다시 CMRR을 구해보자. 이라고 할 수 있다. 아름답다. 오일러 할아버지가 아름답다고 한 숫자 중에 으뜸이 1이다. 이걸 적용하여 다시 CMRR을 구해보자.

어떻게 좀 간략해졌는가? 이 수식이 의미 하는 바는 무엇인가? 저항간의 오차가 작을수록 CMRR은 커진다. 저항의 오차가 없으면 CMRR은 무한대인가? Op Amp. 자체의 CMRR보다는 커질 수 없음을 잘 아셔야 한다. 또한, 차분 증폭기의 증폭 비율이 커지면 커질수록 CMRR은 커진다. 지당한 얘기이겠다. 예를 들자면, 오디오의 볼륨을 높일수록 동상 노이즈 제거는 더 잘된다는 의미이다. 하지만, 1/f 노이즈라든지 다른 노이즈가 커진다는 점은 함정이니, 귀로 잘 듣고 이퀄라이져도 동원하여 본인 자신이 듣기 좋은 상태로 조정하셔야 한다.

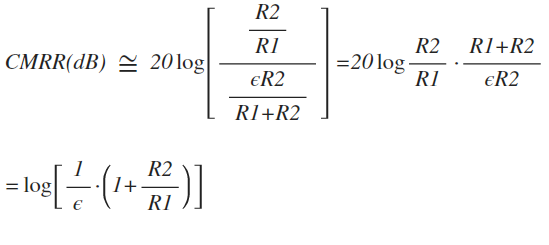

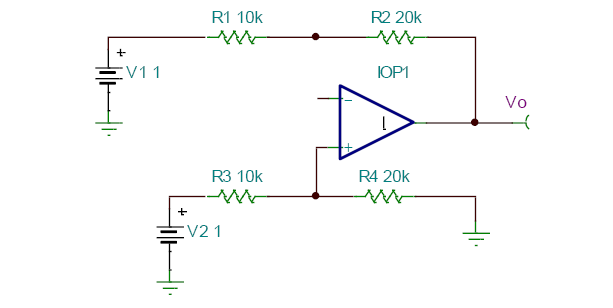

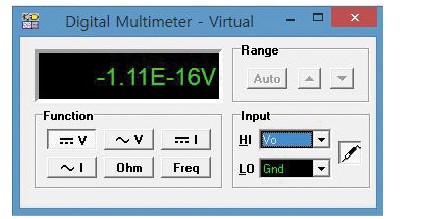

내용이 많이 길어졌지만, CMRR에 대해서는 아무리 강조해도 지나치질 않는다. 그래서, 좀 더 CMRR에 대해서 공부할 필요가 있다. CMRR은 Op Amp.가 제공해주는 축복이다. 이걸 잘 이해하고 있으면 노이즈 억제 회로 설계에 큰 도움을 얻을 수 있다. 간단한 실험 두 가지를 해 보자. 첫번째 실험은 CMRR을 구하는 실험이다. 이상적인 Op Amp.에 이상적인 저항을 연결하여 그림 4-9와 같은 차분증폭기를 꾸미고, 입력 양단에 동일전압 DC 1V를 인가한 후 출력을 확인하여 CMRR을 구하는 것이다.

그림 4-9. CMRR 테스트 회로 그림 4-9처럼 이상적인 Op Amp.로 회로를 꾸민 후 TINA에서 제공하는 멀티미터 기능으로 출력단 전압을 측정해보자. -1.11E-16V가 측정 된다. 작아도 엄청 작다. 의심하시는 분이 계실까봐, 멀티미터 측정 화면을 그림 4-10에 옮겼다.

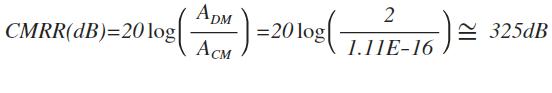

그림 4-10. 그림 4-9회로에서 DC1V 동상 입력시 출력 전압 따라서, ACM=-1.11E-16V이다. 이제 V1에 DC1V 그리고 V2에 DC2V를 인가해서 ADM을 구해보자. 출력이 정확히 2V 나온다. 따라서 ADM=2이다. 정의에 따라, CMRR을 구해보자. *주의. 오차나 증폭비를 대입할 때에는 절대값을 넣어야 한다.

와우! 굉장하다. 구할 때 사실 이미 답이 나왔다. 동상 DC1V 를 인가하니, 출력이 0.111 fV (Femto V) 이다. 펨토(Femto)는 10의 -15승이다. 시뮬레이션이니까 측정가능한 수치이므로, 사실상 0다.

이상적인 Op Amp. 말고 TLC2274와 LM2902를 사용하면 어떨까? CMRR을 동일한 방식으로 각각 구해보자. TLC2274에서는 63.6dB가 나오고 LM2902는 50.0dB가 나온다. 앞서 언급한 제품 설명서의 내용과 많이 다르다. 그 이유는 이 실험이 Op Amp. 자체가 아닌, Op Amp.를 이용한 차분 증폭기를 꾸몄기 때문이다. 하지만, 의외의 결과가 나왔다. 제품 설명서상의 CMRR은 분명 LM2902가 더 컸는데도 불구하고, 차분 증폭기의 CMRR은 TLC2274가 무려 4배이상 (13.6dB) 이상 좋게 나왔다. 왜 이럴까? TINA 오류건 제품 설명서의 오류건 둘 중 하나일텐데, 우리는 Spice 엔진을 사용하는 TINA 결과를 믿고, 즐거운 엔지니어 생활을 영위하도록 하자.

이제 두번째 실험이다. 그림 4-9에서 R2 저항이 1% 오차를 보일 때와 5% 오차를 보일 때, CMRR이 각각 어떻게 변하는지 관찰해보자. TLC2274 선수가 이번 실험에도 수고를 해줬다. 입력 조건은 이전 실험과 동일하다. 1% 오차 실험을 위해R2를 19.8K옴으로 설정했다. 측정결과, CMRR은 51.4dB이다. 많이 떨어졌다. 수식 4-4로 구한 CMRR은 49.5dB이다. 잘 맞아 떨어진다. 이제는 저항 오차를 5%로 설정하고 구해보자. R2를 19K옴으로 정했다. CMRR이 35.8dB 수준으로 훅 떨어졌다. 수식4-4로 구한 값은 35.6dB다. 역시 잘 맞아 떨어진다. 비싼 Op Amp. 사다 놓고, 1원 안되는 돈 아낄려고 오차가 큰 저항을 사용했다가는 Op Amp.의 복음이 널리 전파되는 놀라운 경험을 놓치게 된다. 저항에 돈 좀 쓰자. 그러나 저러나, 심각한 문제가 하나 생겼다. 부품 중에서 가장 단순한 저항을 고르는 작업이 이제는 더 이상 단순한 작업이 아니다. 큰 일이 될 수도 있는 심각한 순간을 여러분은 맞이하고 있는 것이다. 심각하다. 저항을 아무렇게나 가져다가 쓸 일이 전혀 아니다. 어쩌나? 이럴 때, 우리 선배님들께서, 동료 분들께서, 혹은 후배님들께서 나서서 잘 풀어주셨다. 돈만 조금 더 쓰시면 된다. 간혹 R4 위치에 가변저항 (Potentionmeter) 을 달아서 문제를 해결하려 드는 경우도 있는데 필자는 극구 반대한다. 가변저항도 돈이다. 정밀 가변 저항은 더 돈이다. 게다가, 대량 생산하는 품목이라면 어떻게 일일이 조정할 것인가? 게다가 시간에 따라서 그 값도 변하고, 진동 등에 의해서도 값이 바뀌는데 그때마다 조정할 것인가? 정밀 가변 저항 살 돈으로 조금 다른 Op Amp.를 사용해보자. 대부분의 아날로그 반도체 회사들은 이런 문제에 대해 적극적으로 대응하고 있다. Texas Instrumentd 사의 홈페이지인 ti.com에 가보면 ‘Amplifier and Linear’ 라는 제품 카테고리를 발견할 수 있다. 하위 카테고리를 보면, 그림 4-11처럼 ‘Difference Amplifier’항을 발견할 수 있을 것이다.

|

|

그림 4-11. ti.com에서 찾은

Difference Amplifier 메뉴 |

그림 4-12. INA2132의 내부 구조 |

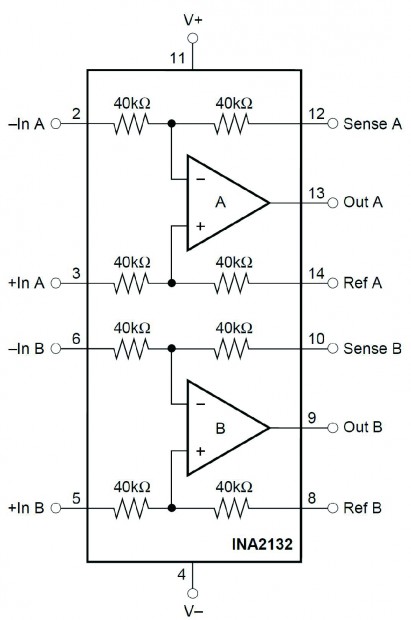

글 쓰는 현재, 총 25종이 Difference Amplifier 범주에 포함되어 있다. 저렴한 제품으로 INA2132가 검색된다. TINA에는 INA2132E라는 라이브러리가 마침 있다. 실험이 가능하니 이 제품을 좀 더 자세히 보도록 해보자. 제품 설명서를 보면, 그림 4-12같은 구조도를 처음 페이지에서 확인할 수 있다.

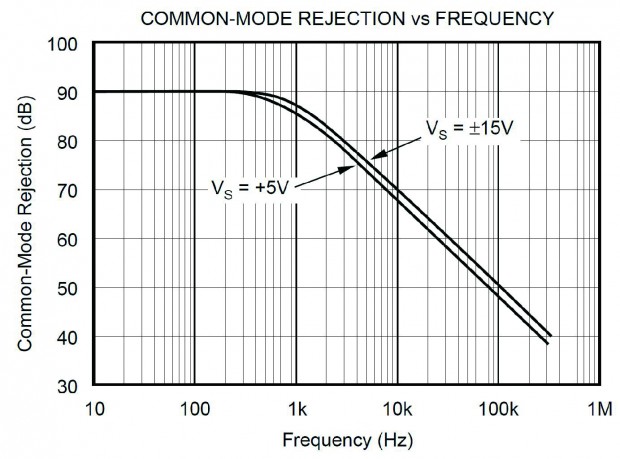

그림 4-12를 보자니, Op Amp. 2개가 보이고, 40K옴 저항이 내장되어 있음을 확인할 수 있다. 그렇다. 정밀/정확 저항을 정밀/정확 반도체 제조 공정에서 구현한 것이다. 이 부분이 다른 Op Amp.와 다른 부분이다. 그림 4-12에서 Sense 핀을 Out 핀에 물리고, Ref 핀을 접지로 만들면 이득이 1배인 차분 증폭기가 만들어 진다. (이 핀들을 왜 만들었는지는 잠시 후 살펴 보기로 하고 지금은 CMRR에 초점을 맞춰서 보자.) 따라서, Sense핀을 출력핀에 연결하고 Ref 핀을 접지에 연결한다고만 우선 받아들이자. 제품 설명서에는 CMRR이 90dB로 나온다. 이 말만 믿으면 안된다. CMRR은 주파수 함수이기에 평탄 대역이 어느 정도되는지 그래프로 살펴봐야 한다. 제품 설명서에서 CMRR 그래프를 발췌했다.

그림 4-13. INA2132의 CMRR 그래프 안타깝게도 10KHz 부근에서는 70dB이하로 나온다. TINA로 앞서 행한 첫번째 실험과 동일한 실험을 해보았다. 동상 DC1V를 인가하니 출력이 27.85uV로 측정된다. CMRR은 91.1dB로 측정된다. 이득이 1배에 불과하지만, CMRR이 무려 91.1dB이다. 대략 낮은 수백 Hz까지의 신호에 대해서는 이런 성능이 유지된다. 대역폭이 아쉽다. 하지만, 이 정도의 CMRR 대역폭은 우수한 편에 속한다.

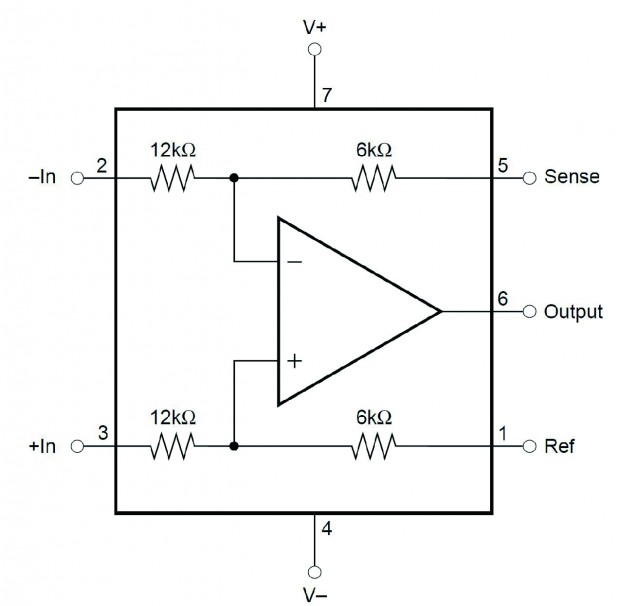

비싼 제품을 한번 골라보자. INA330이 US$2.6 으로 꽤나 비싸다. 그것도 Op Amp.가 하나 들어 있는데 말이다. 그런데 TINA용 라이브러리가 없다. TINA용 라이브러리가 있으면서 가장 비싼 제품으로는 INA157이라는 제품이 검색된다. 살펴보자. CMRR이 86dB에 그친다. 그런데 왜 비싼걸까? 속도가 매우 빠르고, 기타 다른 지표들이 좀 더 우수한 듯하고, 나온지가 제법 되어서 비싼 듯도 하다. 다음은 내부 구조도다.

그림 4-14. INA157 내부구조 이득을 결정하는 저항이 12K와 6K이다. Sense 핀에다가 V1을 입력하고, -In을 Output에 연결하고, +In 핀을 접지에 연결한 후, Ref에다가 V2를 입력하면 이득 2배짜리가 된다. 반대로 하면 1/2배가 된다. 재미지구나. 이득을 2배로 설정하고 TINA를 이용해 CMRR을 구해보면 91.2dB를 얻을 수 있다. 비록 제품 설명서 상으로는 INA2132가 우세했지만 실제 실험에서는 INA157이 이득을 2배로 설정할 수 있기에, 좋은 결과가 나온 것도 같다. 참고로 TINA에서 Difference Amplifier 모델을 추가하려면 다음의 아이콘을 눌러야 한다.

그림 4-15. TINA에서 차분증폭기 모델 추가하기 그런데, INA157이 왜 비쌀까? 비싸면, CMRR도 좋아야 할 것 아닌가? 그렇다. CMRR 그래프를 보도록 하자. 주파수에 신경을 바짝 세워서 그래프를 주시해주시기 바란다.

그림 4-16. INA157의 CMRR 그래프 거의 70 KHz까지 CMRR이 유지된다. 이런 Op Amp. 잘 없다. 따라서, 값싼 INA2132를 사용할 것인가, 비싼 INA157을 사용할 것인가 하는 문제는 다루는 신호의 대역폭에 따라 결정되는 것이다. 만약 HiFi 오디오를 설계한다면, 당연 INA157이다. 회로에 외부에서 유입되는 노이즈가 많다면 당연히 INA157이다. 그런데, 상대적으로 너무 비싸다. 형편에 맞게 잘 선정하시길 바란다.

실제 부품을 예로 들어가면서까지 CMR 기능에 대해서 살펴보았다. 무엇보다도, Common Mode Rejection 기능을 잘 사용하는 것이 Op Amp.를 제대로 사용하는 것이라고 말할 수 있다. 그래서 이 절이 이토록 긴 것이다. CMR 기능을 잘 사용하려면, 입력을 차동으로 받아들여야 한다. 입력이 단동(Single Ended) 일 경우에는 CMR 기능을 활용하기가 어렵다. 차동이 아니면 차분이라도 하는 것이 좋다. 그래서, Op Amp.의 두 입력단으로 연결되는 각각의 선을 최대한 가까이 붙이고 동일한 길이와 동일한 임피던스 성분으로 구성한다면 신호 전송선에 유입되는 외부 노이즈는 동상일 가능성이 높기에 걸러낼 수 있다. 단순히 동일한 두 신호선만으로 동상 성격의 노이즈를 걸러 내는 행위는 고성능 아날로그 회로를 설계하는데 있어서 기본 중의 기본이다. 그림 4-16을 다시보자. 200KHz에서 CMRR이 약 80dB이다. 별 다른 필터를 사용하지 않아도, 입력 양단에 유입되는1V 크기의 노이즈는 0.1mV로 쪼그라들어 버린다. 오로지 Op Amp.를 제대로만 사용했다면 기대할 수 있는 대단한 노이즈 억제 능력인 것이다. 좋지 아니한가? 비싼 돈 주고 산 Op Amp.를 놀릴 것인가? 어렵게 생각할 필요없다. 좋은 저항으로 대칭을 잘 이뤄서 증폭기를 설계하면 높은 CMRR을 기대할 수 있다. 그래서, Op Amp.가 더더욱 좋은 것이고, 디지털 회로 세상에서도 Op Amp.의 위상은 더욱 더 공고해지고 있는 것이다.

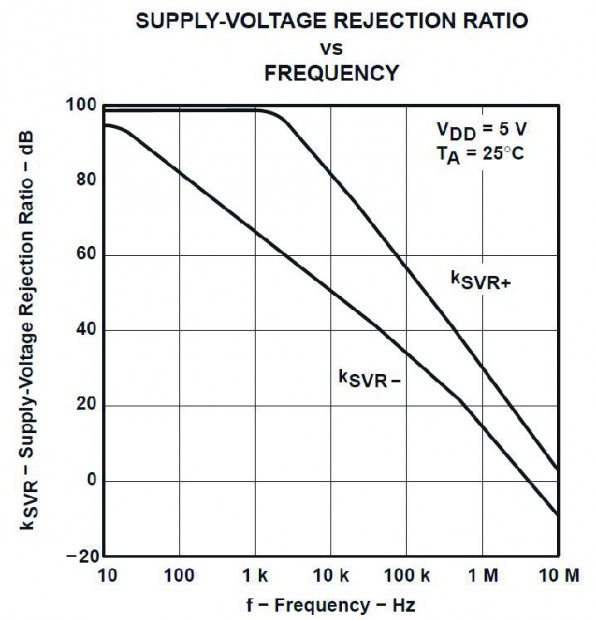

이 정도로 해서 CMRR을 마무리 짓고, 다음 주제인 PSRR로 넘어가자. 끝 글자들이 RR로 끝나기에 라임이 잘 맞아 떨어져서 힙합가사라도 쓰나 하시겠지만, 같다고도 볼 수 있고 다르다라고도 볼 수 있는 RR이다. PSRR는 Power Supply Ripple Rejection Ratio 이다. 이렇게도 쓴다. Power Supply Rejection Ratio. 전자가 더 명확하고, 따라서, PSRRR이 맞지만 CMRR과 운율이 안 맞기에 탈락시킨듯 하다. 운율맞게 우리도PSRR 이라고 하자.

PSRR을 측정하기 위해서, Op Amp. 전원핀에 60Hz, 혹은 120Hz 정현파를 공급 전압에 섞어서 공급한다. 출력단에서 60Hz 혹은 120Hz 정현파 성분을 측정한 후 dB로 표현한 것이 PSRR이다. 60Hz나 120Hz는 교류 전원을 의미한다. 간단한 실험을 한번 해보자. TLC2274로 2배짜리 차분 증폭기를 그림 4-9처럼 꾸민 후, V+ 단자에 5V를 공급한다. Ripple을 구현하기 위해서, 5V DC 전원에 + 1Vpp, 60Hz 정현파를 더해서 공급한다. 양 입력단에는 DC1V를 인가한다. 그리고 오실로스코프로 출력을 관찰한다. 출력 파형에서 관찰되는 리플의 Vpp를 구하여 60Hz, 1Vpp 정현파와 비를 구한 후, 20log를 취하면 PSRR 이 얻어진다. TINA로 시뮬레이션을 해보니, 출력으로 약 140uVpp, 60Hz 정현파가 관찰된다. 따라서, PSRR은 77.1dB 이다. 상당히 우수하다. 따라서, Op Amp.를 사용하신다면, 60Hz 전원 노이즈로 인한 걱정은 접어두셔도 되겠다. 하지만, Op Amp. 앞 단에 저항이나 커패시터가 접지나 전원단에 직접 연결된 회로가 존재한다면 이것은 또 다른 문제다. Op Amp.의 입력 신호에 전원 노이즈가 섞여서 들어온다면, 5장에서 배울 Notch 필터로 제거해야 한다. TLC2274의 제품 설명서에 명시된 PSRR은 통상 95dB 수준이고 최저 80dB 수준이다. 제품 설명서에는 측정 환경에 대한 언급은 없다. TINA 실험은 일반적인 사용 예를 가지고 행한 것이기에 실질적으로는 TINA로 행한 실험이 적용될 것이다. 제품 설명서에서 명시한 수치에 비해 모자라지만, 77dB라는 수치는 결코 나쁜 수치가 아니다. 참고로, 이득이 높아지면, 출력에 나오는 전원 노이즈 성분도 커지기에 PSRR 수치는 낮아진다는 점을 유의해야 한다. 그렇다면, 전원단에 광대역 노이즈가 유입되고 있다면 어떨까? PSRR에 관한 그래프도 제품 설명서에 나와있으니 유심히 보시기 바란다. 역시 주파수에 대한 함수이다. 다음은 TLC2274의 PSRR 그래프이다.

그림 4-17. TLC2274의 PSRR 안타깝게도, 전원노이즈 제거 대역폭이 그다지 넓지 않다. 특히, 음의 전원 쪽 PSRR의 대역폭이 많이 좁다. 이를 극복하는 별다른 방법은 없다. 구현하고자 하는 시스템의 전원단을 잘 설계해야 할 것이며, Op Amp. 전원 핀에 바이패쓰(Bypass) 커패시터를 잘 달아주는 것이 거의 최선의 방법이라 하겠다.

다음 시간에는 5. Loading Effect (부하의 영향)

6. Instrumentation Amplifier (정밀 기기용, 계측용 증폭기)

7. Op Amp.의 Sense 핀과 Ref. 핀의 사용법에 대하여 살펴보도록 하겠습니다.

|